# ACPL-064L, ACPL-M61L, ACPL-W61L, ACPL-K64L

Low-Power 10-MBd Digital CMOS Optocouplers

### **Data Sheet**

### **Description**

The Broadcom® low-power ACPL-x6xL digital optocouplers combine an AlGaAs light emitting diode (LED) and an integrated high gain photodetector. The optocoupler consumes low power, at maximum 1.3 mA I<sub>DD</sub> current per channel across temperature. With a forward LED current as low as 1.6 mA, most microprocessors can directly drive the LED.

An internal Faraday shield provides a guaranteed common-mode transient immunity specification of 20 kV/µs. Maximum AC and DC circuit isolation is achieved while maintaining TTL/CMOS compatibility.

The optocouplers' CMOS outputs are slew-rate controlled and designed to allow the rise and fall time to be controlled over a wide load-capacitance range.

The ACPL-x6xL series operates from both 3.3V and 5V supply voltages with guaranteed AC and DC performance from  $-40^{\circ}$ C to  $+105^{\circ}$ C.

These low-power optocouplers are suitable for high speed logic interface applications.

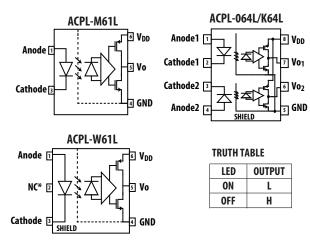

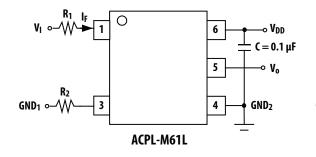

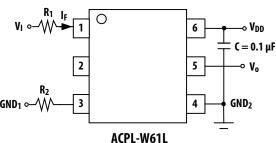

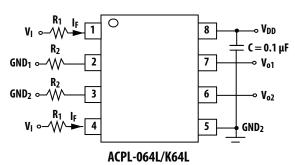

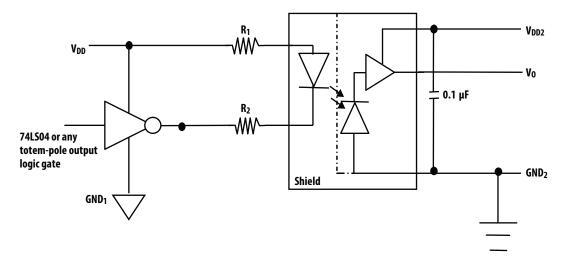

### **Functional Diagrams**

A 0.1  $\mu F$  bypass capacitor must be connected as close as possible between pins  $\,V_{DD}$  and GND.

#### **Features**

- Low I<sub>DD</sub> current: 1.3 mA/channel maximum

- Low input current: 1.6 mA

- Built-in slew-rate controlled outputs

- 20 kV/ $\mu$ s minimum Common-Mode Rejection (CMR) at  $V_{CM} = 1000V$

- High speed: 10 MBd minimum

- Guaranteed AC and DC performance over wide temperature: -40°C to +105°C

- Wide package selection: SO-5, SO-8, stretched SO-6, and stretched SO-8

- Safety approval

- UL 1577 recognized: 3750V<sub>rms</sub> for 1 minute for ACPL-064L/M61L and 5000V<sub>rms</sub> for 1 minute for ACPL-W61L/K64L

- CSA approval

- IEC/EN/DIN EN 60747-5-5 approval for Reinforced Insulation

- RoHS-compliant

### **Applications**

- Communication interfaces: RS485, CANBus, and I<sup>2</sup>C

- Microprocessor system interfaces

- Digital isolation for A/D and D/A converters

#### **CAUTION**

It is advised that normal static precautions be taken in handling and assembly of this component to prevent damage and/or degradation which may be induced by ESD. The components featured in this data sheet are not to be used in military or aerospace applications or environments.

### **Ordering Information**

The ACPL-064L and ACPL-M61L are UL recognized with an isolation voltage of  $3750V_{rms}$  for 1 minute per UL1577. The ACPL-W61L and ACPL-K64L are UL recognized with an isolation voltage of  $5000V_{rms}$  for 1 minute per UL1577. All devices are RoHS-compliant.

| Part Number | Option<br>RoHS-Compliant | Package   | Surface Mount | Tape and Reel | UL1577 5000<br>Vrms /1 Minute<br>Rating | IEC/EN/DIN EN<br>60747-5-5 | Quantity      |

|-------------|--------------------------|-----------|---------------|---------------|-----------------------------------------|----------------------------|---------------|

| ACPL-M61L   | -000E                    | SO-5      | Х             |               |                                         |                            | 100 per tube  |

|             | -060E                    |           | Х             |               |                                         | X                          | 100 per tube  |

|             | -500E                    |           | Х             | Х             |                                         |                            | 1500 per reel |

|             | -560E                    |           | Х             | Х             |                                         | Х                          | 1500 per reel |

| ACPL-064L   | -000E                    | SO-8      | Х             |               |                                         |                            | 100 per tube  |

|             | -060E                    |           | Х             |               |                                         | Х                          | 100 per tube  |

|             | -500E                    |           | Х             | Х             |                                         |                            | 1500 per reel |

|             | -560E                    |           | Х             | Х             |                                         | Х                          | 1500 per reel |

| ACPL-W61L   | -000E                    | Stretched | Х             |               | Х                                       |                            | 100 per tube  |

|             | -060E                    | S06       | Х             |               | Х                                       | Х                          | 100 per tube  |

|             | -500E                    |           | Х             | Х             | Х                                       |                            | 1000 per reel |

|             | -560E                    |           | Х             | Х             | Х                                       | Х                          | 1000 per reel |

| ACPL-K64L   | -000E                    | Stretched | Х             |               | Х                                       |                            | 80 per tube   |

|             | -060E                    | S08       | Х             |               | Х                                       | Х                          | 80 per tube   |

|             | -500E                    |           | Х             | Х             | Х                                       |                            | 1000 per reel |

|             | -560E                    |           | Х             | Х             | Х                                       | Х                          | 1000 per reel |

To form an ordering part number, choose a part number from the part number column and combine it with the desired option from the RoHS option column.

#### **Example:**

Part number ACPL-M61L-560E describes an optocoupler with a surface mount SO-5 package; delivered in Tape and Reel with 1500 parts-per-reel; with IEC/EN/DIN EN 60747-5-5 Safety Approval; and full RoHS compliance.

Option data sheets are available. Contact your Broadcom sales representative or authorized distributor for information.

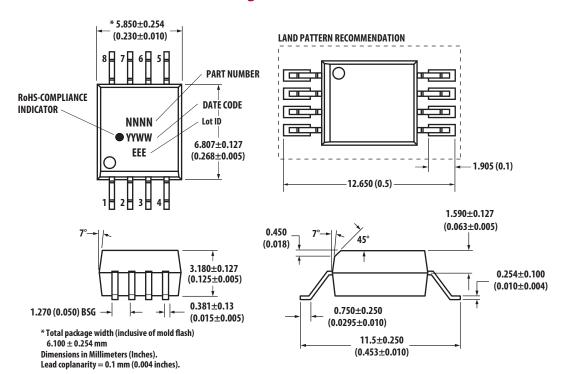

### **Package Outline Drawings**

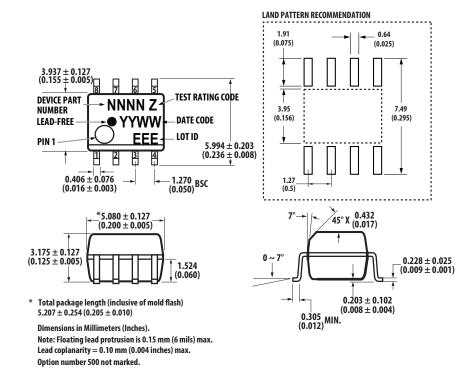

### **ACPL-064L SO-8 Package**

### **ACPL-M61L SO-5 Package**

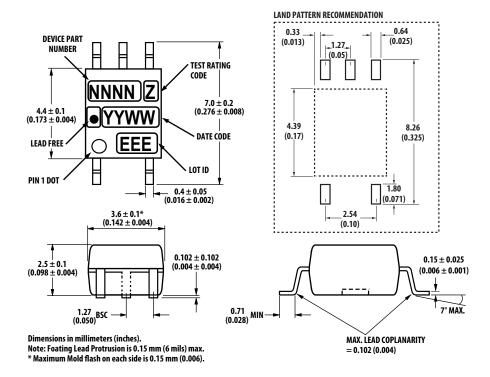

### **ACPL-W61L Stretched SO-6 Package**

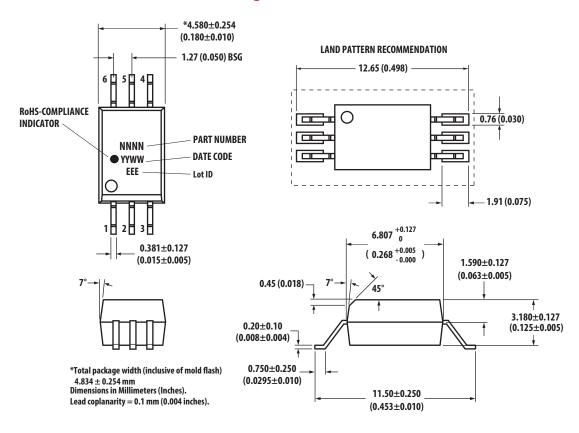

### **ACPL-K64L Stretched SO-8 Package**

### **Reflow Soldering Profile**

The recommended reflow soldering conditions are per JEDEC Standard J-STD-020 (latest revision). Non-halide flux should be used.

### **Regulatory Information**

The ACPL-064L, ACPL-M61L, ACPL-W61L, and ACPL-K64L are approved by the following organizations:

- IEC/EN/DIN EN 60747-5-5 (Option 060 only)

- **UL** Approval under UL 1577 component recognition program up to  $V_{ISO} = 3750V_{rms}$  for the ACPL-M61L/064L and  $V_{ISO} = 5000V_{rms}$  for the ACPL-W61L/K64L File E55361.

- CSA Approval under CSA Component Acceptance Notice #5, File CA 88324.

### **Insulation and Safety Related Specifications**

| Parameter                                            | Symbol | ACPL-064L | ACPL-M61L | ACPL-W61L<br>ACPL-K64L | Unit | Conditions                                                                                                                         |

|------------------------------------------------------|--------|-----------|-----------|------------------------|------|------------------------------------------------------------------------------------------------------------------------------------|

| Minimum External Air Gap<br>(External Clearance)     | L(101) | 4.9       | 5         | 8                      | mm   | Measured from input terminals to output terminals, shortest distance through air.                                                  |

| Minimum External Tracking<br>(External Creepage)     | L(102) | 4.8       | 5         | 8                      | mm   | Measured from input terminals to output terminals, shortest distance path along body.                                              |

| Minimum Internal Plastic Gap<br>(Internal Clearance) |        | 0.08      | 0.08      | 0.08                   | mm   | Through insulation distance conductor to conductor, usually the straight line distance thickness between the emitter and detector. |

| Tracking Resistance<br>(Comparative Tracking Index)  | СТІ    | 175       | 175       | 175                    | V    | DIN IEC 112/VDE 0303 Part 1.                                                                                                       |

| Isolation Group                                      |        | Illa      | Illa      | Illa                   |      | Material Group (DIN VDE 0110, 1/89, Table 1)                                                                                       |

### IEC/EN/DIN EN 60747-5-5 Insulation Characteristics<sup>a</sup> (Option 060)

|                                                                                                            |                        | Charae                  |                         |                   |

|------------------------------------------------------------------------------------------------------------|------------------------|-------------------------|-------------------------|-------------------|

| Description                                                                                                | Symbol                 | ACPL-064L/<br>ACPL-M61L | ACPL-W61L/<br>ACPL-K64L | Unit              |

| Installation classification per DIN VDE 0110/39, Table 1                                                   |                        |                         |                         |                   |

| for rated mains voltage ≤ 150V <sub>rms</sub>                                                              |                        | I – IV                  | I – IV                  |                   |

| for rated mains voltage ≤ 300V <sub>rms</sub>                                                              |                        | I – IV                  | I – IV                  |                   |

| for rated mains voltage ≤ 600V <sub>rms</sub>                                                              |                        | I – III                 | I – IV                  |                   |

| for rated mains voltage ≤ 1000V <sub>rms</sub>                                                             |                        |                         | I – III                 |                   |

| Climatic Classification                                                                                    |                        | 55/105/21               | 55/105/21               |                   |

| Pollution Degree (DIN VDE 0110/39)                                                                         |                        | 2                       | 2                       |                   |

| Maximum Working Insulation Voltage                                                                         | V <sub>IORM</sub>      | 567                     | 1140                    | $V_{peak}$        |

| Input to Output Test Voltage, Method b <sup>a</sup>                                                        | V <sub>PR</sub>        | 1063                    | 2137                    | $V_{peak}$        |

| $V_{IORM} \times 1.875 = V_{PR}$ , 100% Production Test with $t_m = 1s$ ,<br>Partial discharge < 5 pC      |                        |                         |                         |                   |

| Input to Output Test Voltage, Method a <sup>a</sup>                                                        | $V_{PR}$               | 907                     | 1824                    | V <sub>peak</sub> |

| $V_{IORM} \times 1.6 = V_{PR}$ , Type and Sample Test, $t_m = 10s$ ,<br>Partial discharge $< 5 \text{ pC}$ |                        |                         |                         |                   |

| Highest Allowable Overvoltage (Transient Overvoltage t <sub>ini</sub> = 60s)                               | V <sub>IOTM</sub>      | 6000                    | 8000                    | $V_{peak}$        |

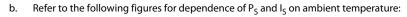

| Safety-Limiting Values – maximum values allowed in the event of a failure                                  |                        |                         |                         |                   |

| Case Temperature                                                                                           | T <sub>S</sub>         | 150                     | 175                     | °C                |

| Input Current <sup>b</sup>                                                                                 | I <sub>S, INPUT</sub>  | 150                     | 230                     | mA                |

| Output Power <sup>b</sup>                                                                                  | P <sub>S, OUTPUT</sub> | 600                     | 600                     | mW                |

| Insulation Resistance at T <sub>S</sub> , V <sub>IO</sub> = 500V                                           | R <sub>S</sub>         | >10 <sup>9</sup>        | >10 <sup>9</sup>        | Ω                 |

a. Refer to the optocoupler section of the Isolation and Control Components Designer's Catalog, under Product Safety Regulations section, (IEC/EN/DIN EN 60747-5-5) for a detailed description of Method a and Method b partial discharge test profiles.

**NOTE** These optocouplers are suitable for *safe electrical isolation* only within the safety limit data. Maintenance of the safety data shall be ensured by means of protective circuits.

### **Absolute Maximum Ratings**

| Parameter                                             | Symbol               | Min  | Max                                        | Unit | Condition                              |  |  |

|-------------------------------------------------------|----------------------|------|--------------------------------------------|------|----------------------------------------|--|--|

| Storage Temperature                                   | T <sub>S</sub>       | -55  | +125                                       | °C   |                                        |  |  |

| Operating Temperature                                 | T <sub>A</sub>       | -40  | +105                                       | °C   |                                        |  |  |

| Reverse Input Voltage                                 | V <sub>R</sub>       | _    | 5                                          | V    |                                        |  |  |

| Supply Voltage                                        | $V_{DD}$             | _    | 6.5                                        | V    |                                        |  |  |

| Average Forward Input Current                         | I <sub>F</sub>       | _    | 8                                          | mA   |                                        |  |  |

| Peak Forward Input Current                            | I <sub>F(TRAN)</sub> | _    | 1                                          | Α    | ≤ 1-µs Pulse Width, <300 pulses/second |  |  |

| (I <sub>F</sub> at 1-μs pulse width, <10% duty cycle) |                      |      | 80                                         | mA   | ≤ 1-µs Pulse Width, <10% Duty Cycle    |  |  |

| Output Current                                        | Io                   | _    | 10                                         | mA   |                                        |  |  |

| Output Voltage                                        | V <sub>O</sub>       | -0.5 | V <sub>DD</sub> + 0.5                      | V    |                                        |  |  |

| Input Power Dissipation                               | P <sub>I</sub>       | _    | 14                                         | mW   |                                        |  |  |

| Output Power Dissipation                              | P <sub>O</sub>       | _    | 20                                         | mW   |                                        |  |  |

| Lead Solder Temperature                               | T <sub>LS</sub>      | _    | 260°C for 10s., 1.6 mm below seating plane |      |                                        |  |  |

| Solder Reflow Temperature Profile                     |                      |      | See Package Outline Drawings.              |      |                                        |  |  |

### **Recommended Operating Conditions**

| Parameter                 | Symbol               | Min | Max  | Unit |

|---------------------------|----------------------|-----|------|------|

| Operating Temperature     | T <sub>A</sub>       | -40 | +105 | °C   |

| Input Current, Low Level  | I <sub>FL</sub>      | 0   | 250  | μΑ   |

| Input Current, High Level | I <sub>FH</sub>      | 1.6 | 6.0  | mA   |

| Power Supply Voltage      | V <sub>DD</sub>      | 2.7 | 5.5  | V    |

| Forward Input Voltage     | V <sub>F (OFF)</sub> | _   | 0.8  | V    |

### **Electrical Specifications (DC)**

Over the recommended temperature ( $T_A = -40$ °C to +105°C) and supply voltage (2.7V  $\leq V_{DD} \leq 5.5$ V). All typical specifications are at  $V_{DD} = 5$ V and  $T_A = 25$ °C.

| Parameter                              | Symbol                    | Channel | Min                   | Тур      | Max | Unit  | Test Conditions                                                                                |

|----------------------------------------|---------------------------|---------|-----------------------|----------|-----|-------|------------------------------------------------------------------------------------------------|

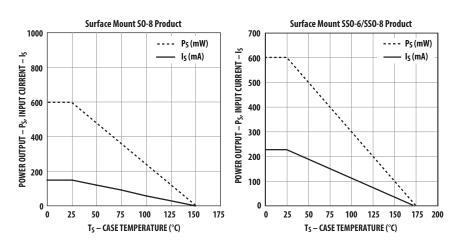

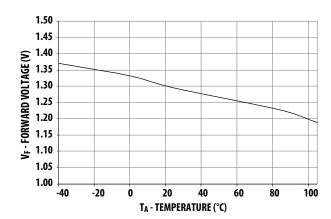

| Input Forward Voltage                  | V <sub>F</sub>            |         | 0.95                  | 1.3      | 1.7 | V     | I <sub>F</sub> = 2 mA; Figure 1 and Figure 2                                                   |

| Input Reverse Breakdown Voltage        | BV <sub>R</sub>           |         | 3                     | 5        | _   | V     | Ι <sub>R</sub> = 10 μΑ                                                                         |

| Logic High Output Voltage              | V <sub>OH</sub>           |         | V <sub>DD</sub> – 0.1 | $V_{DD}$ | _   | V     | $I_F$ = 0 mA, $V_I$ = 0V ( $R_T$ = 1.68 kΩ)<br>or ( $R_T$ = 870Ω), $I_O$ = -20 μA              |

|                                        |                           |         | V <sub>DD</sub> – 1.0 | $V_{DD}$ | _   | V     | $I_F$ = 0 mA, $V_I$ = 0V ( $R_T$ = 1.68 kΩ)<br>or ( $R_T$ = 870Ω), $I_O$ = -3.2 mA             |

| Logic Low Output Voltage               | V <sub>OL</sub>           |         | _                     | 0.03     | 0.1 | V     | $I_F$ = 2 mA, $V_I$ = 5V ( $R_T$ = 1.68 kΩ)<br>or $V_I$ = 3.3V ( $R_T$ = 870Ω), $I_O$ = 20 μA  |

|                                        |                           |         | _                     | 0.18     | 0.4 | V     | $I_F$ = 2 mA, $V_I$ = 5V ( $R_T$ = 1.68 kΩ)<br>or $V_I$ = 3.3V ( $R_T$ = 870Ω), $I_O$ = 3.2 mA |

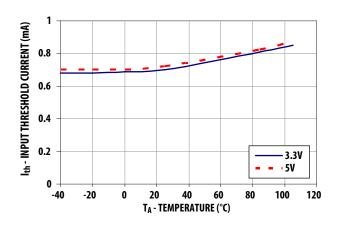

| Input Threshold Current                | I <sub>TH</sub>           |         | _                     | 0.7      | 1.3 | mA    | Figure 3                                                                                       |

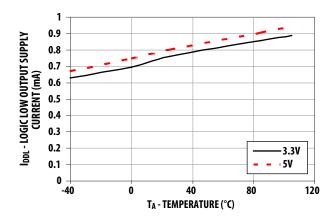

| Logic Low Output Supply Current        | I <sub>DDL</sub>          | Single  | _                     | 0.8      | 1.3 | mA    | Figure 4                                                                                       |

|                                        |                           | Dual    | _                     | 1.6      | 2.6 | 1     |                                                                                                |

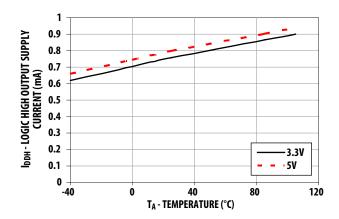

| Logic High Output Supply Current       | I <sub>DDH</sub>          | Single  | _                     | 0.8      | 1.3 | mA    | Figure 5                                                                                       |

|                                        |                           | Dual    | _                     | 1.6      | 2.6 | 1     |                                                                                                |

| Input Capacitance                      | C <sub>IN</sub>           |         | _                     | 60       | _   | pF    | $f = 1 \text{ MHz}, V_F = 0V$                                                                  |

| Input Diode Temperature<br>Coefficient | $\Delta V_F / \Delta T_A$ |         | _                     | -1.6     | _   | mV/°C | I <sub>F</sub> = 2 mA                                                                          |

### **Switching Specifications (AC)**

Over the recommended temperature ( $T_A = -40^{\circ}\text{C}$  to  $+105^{\circ}\text{C}$ ) and supply voltage ( $2.7\text{V} \le \text{V}_{DD} \le 5.5\text{V}$ ). All typical specifications are at  $\text{V}_{DD} = 5\text{V}$  and  $T_A = 25^{\circ}\text{C}$ .

| Parameter                                                               | Symbol           | Min | Тур | Max | Unit  | Test Conditions                                                                                                                                                                                                                                                                            |

|-------------------------------------------------------------------------|------------------|-----|-----|-----|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Propagation Delay Time to Logic Low Output <sup>a</sup>                 | t <sub>PHL</sub> | _   | 46  | 80  | ns    | $I_F = 2 \text{ mA}, V_I = 5V, R_T = 1.68 \text{ k}\Omega,$                                                                                                                                                                                                                                |

| Propagation Delay Time to Logic High Output <sup>a</sup>                | t <sub>PLH</sub> | _   | 40  | 80  | ns    | $C_L = 15$ pF, CMOS Signal Levels.<br>$I_F = 2$ mA, $V_I = 3.3V$ , $R_T = 870\Omega$ ,                                                                                                                                                                                                     |

| Pulse Width                                                             | t <sub>PW</sub>  | 100 | _   | _   | ns    | $C_L = 15 \text{ pF, CMOS Signal Levels.}$                                                                                                                                                                                                                                                 |

| Pulse Width Distortion <sup>b</sup>                                     | PWD              | _   | 6   | 30  | ns    | Figure 6 and Figure 7                                                                                                                                                                                                                                                                      |

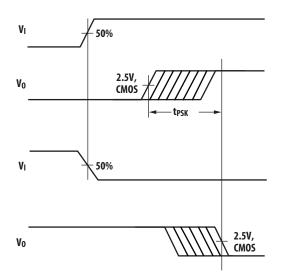

| Propagation Delay Skew <sup>c</sup>                                     | t <sub>PSK</sub> | _   |     | 30  | ns    |                                                                                                                                                                                                                                                                                            |

| Output Rise Time (10% to 90%)                                           | t <sub>R</sub>   | _   | 12  | _   | ns    | $I_F$ = 2 mA, $V_I$ = 5V, $R_T$ = 1.68 kΩ, $C_L$ = 15 pF, CMOS Signal Levels.                                                                                                                                                                                                              |

|                                                                         |                  | _   | 10  | _   | ns    | $I_F = 2$ mA, $V_I = 3.3$ V, $R_T = 870\Omega$ , $C_L = 15$ pF, CMOS Signal Levels.                                                                                                                                                                                                        |

| Output Fall Time (90% to 10%)                                           | t <sub>F</sub>   | _   | 12  | _   | ns    | $I_F = 2$ mA, $V_I = 5V$ , $R_T = 1.68$ kΩ, $C_L = 15$ pF, CMOS Signal Levels.                                                                                                                                                                                                             |

|                                                                         |                  | _   | 10  | _   | ns    | $I_F = 2$ mA, $V_I = 3.3$ V, $R_T = 870\Omega$ , $C_L = 15$ pF, CMOS Signal Levels.                                                                                                                                                                                                        |

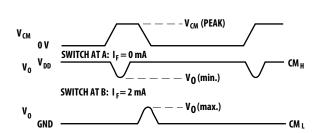

| Static Common-Mode Transient Immunity at Logic High Output <sup>d</sup> | CM <sub>H</sub>  | 20  | 35  | _   | kV/μs | $\begin{split} &V_{CM}=1000\text{V}, T_{A}=25^{\circ}\text{C}, I_{F}=0\text{ mA},\\ &V_{I}=0\text{V }(R_{T}=1.68\text{ k}\Omega)\text{ or }(R_{T}=870\Omega),\\ &C_{L}=15\text{ pF, CMOS Signal Levels.} \end{split}$ Figure 8                                                             |

| Static Common-Mode Transient Immunity at Logic Low Output <sup>e</sup>  | CM <sub>L</sub>  | 20  | 35  | _   | kV/μs | $V_{CM} = 1000V$ , $T_A = 25^{\circ}C$ , $V_I = 5 V$<br>$(R_T = 1.68 \text{ k}\Omega) \text{ or } V_I = 3.3V$<br>$(R_T = 870\Omega)$ , $I_F = 2 \text{ mA}$ , $C_L = 15 \text{ pF}$ ,<br>CMOS Signal Levels.<br>Figure 8                                                                   |

| Dynamic Common-Mode Transient Immunity <sup>f</sup>                     | CMR <sub>D</sub> | _   | 35  | _   | kV/μs | $\begin{split} &V_{CM}=1000\text{ V}, T_A=25^{\circ}\text{C}, I_F=2\text{ mA},\\ &V_I=5\text{V} \ (R_T=1.68\text{ k}\Omega) \text{ or } V_I=3.3\text{ V}\\ &(R_T=870\Omega), 10\text{ MBd datarate,}\\ &\text{the absolute increase of PWD} < 10\text{ ns}\\ &\text{Figure 8} \end{split}$ |

a.  $t_{PHL}$  propagation delay is measured from the 50% ( $V_{in}$  or  $I_F$ ) on the rising edge of the input pulse to the 50%  $V_{DD}$  of the falling edge of the  $V_O$  signal.  $t_{PLH}$  propagation delay is measured from the 50% ( $V_{in}$  or  $I_F$ ) on the falling edge of the input pulse to the 50% level of the rising edge of the  $V_O$  signal.

- d. CM<sub>H</sub> is the maximum tolerable rate of rise of the common-mode voltage to assure that the output remains in a high logic state.

- e. CM<sub>1</sub> is the maximum tolerable rate of fall of the common-mode voltage to assure that the output remains in a low logic state.

- f. CM<sub>D</sub> is the maximum tolerable rate of the common-mode voltage during data transmission to assure that the absolute increase of the PWD is less than 10 ns.

b. PWD is defined as  $|t_{PHL} - t_{PLH}|$ .

c.  $t_{PSK}$  is equal to the magnitude of the worst-case difference in  $t_{PHL}$  and/or  $t_{PLH}$  that is seen between units at any given temperature within the recommended operating conditions.

### **Package Characteristics**

All typicals are at  $T_A = 25$ °C.

| Parameter                | Symbol           | Part Number            | Min  | Тур              | Max | Unit             | Test Conditions                              |

|--------------------------|------------------|------------------------|------|------------------|-----|------------------|----------------------------------------------|

| Input-Output Insulation  | V <sub>ISO</sub> | ACPL-064L<br>ACPL-M61L | 3750 | _                | _   | V <sub>rms</sub> | RH < 50% for 1 min.<br>T <sub>A</sub> = 25°C |

|                          |                  | ACPL-W61L<br>ACPL-K64L | 5000 | _                | _   |                  |                                              |

| Input-Output Resistance  | R <sub>I-O</sub> |                        | _    | 10 <sup>12</sup> | _   | Ω                | V <sub>I-O</sub> = 500V                      |

| Input-Output Capacitance | C <sub>I-O</sub> |                        | _    | 0.6              | _   | pF               | f = 1 MHz, T <sub>A</sub> = 25°C             |

Figure 1 Typical Input Diode Forward Current Characteristic

Figure 2 Typical V<sub>F</sub> versus Temperature

Figure 3 Typical Input Threshold Current versus Temperature

Figure 4 Typical Logic Low Output Supply Current (Per Channel) versus Temperature

Figure 5 Typical Logic High Output Supply Current (Per Channel) versus Temperature

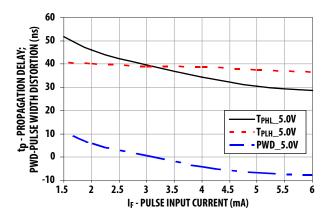

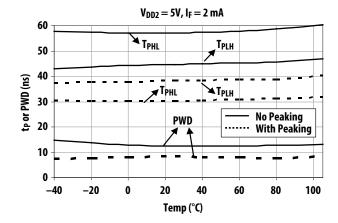

Figure 6 Typical Switching Speed versus Pulse Input with a 5V Supply Voltage

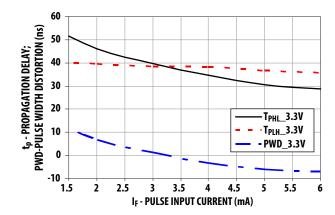

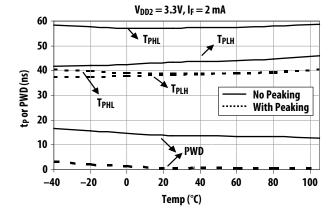

Figure 7 Typical Switching Speed versus Pulse Input Current with a 3.3V Supply Voltage

### Supply Bypassing, LED Bias Resistors, and PC Board Layout

The ACPL-x6xL optocouplers are extremely easy to use and feature high-speed, push-pull CMOS outputs. Pull-up resistors are not required.

The external components required for proper operation are the input limiting resistors and the output bypass capacitor. Capacitor values should be  $0.1 \mu F$  and should be placed as close as possible to the power-supply pins of the optocoupler.

For ACPL-M61L/W61L:

$$\begin{split} V_1 &= 3.3V; \, R_1 = 510\Omega \pm 1\%, \, R_2 = 360\Omega \pm 1\% \\ V_1 &= 5.0V; \, R_1 = 1000\Omega \pm 1\%, \, R_2 = 680\Omega \pm 1\% \\ R_T &= R_1 + R_2 \quad R_1/R_2 = 1.5 \end{split}$$

For ACPL-064L/K64L:

$$V_1 = 3.3V$$

:  $R_1 = 430\Omega \pm 1\%$ ,  $R_2 = 430\Omega \pm 1\%$

$V_1 = 5.0V$ :  $R_1 = 845\Omega \pm 1\%$ ,  $R_2 = 845\Omega \pm 1\%$

$R_T = R_1 + R_2$   $R_1/R_2 = 1$

Figure 8 Recommended PCB Layout and Input Current-Limiting Resistor Selection

Anode

Shield

Vo

Output

Monitoring

node

Pulse Gen

3.3V/5V

# Propagation Delay, Pulse-Width Distortion, and Propagation Delay Skew

Propagation delay is a figure of merit that describes how quickly a logic signal propagates through a system. The propagation delay from low-to-high (t<sub>PLH</sub>) is the amount of time required for an input signal to propagate to the output, causing the output to change from low to high.

Similarly, the propagation delay from high-to-low ( $t_{PHL}$ ) is the amount of time required for the input signal to propagate to the output, causing the output to change from high-to-low (see Figure 9).

Pulse-width distortion (PWD) results when  $t_{PLH}$  and  $t_{PHL}$  differ in value. PWD is defined as the difference between  $t_{PLH}$  and  $t_{PHL}$ . PWD determines the maximum data rate of a transmission system. PWD can be expressed in percent by dividing the PWD (in ns) by the minimum pulse width (in ns) being transmitted. Typically, a PWD of 20% to 30% of the minimum pulse width is tolerable; the exact figure depends on the particular application (RS232, RS422, T-1, etc.).

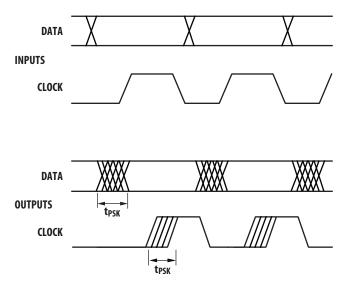

Propagation delay skew, t<sub>PSK</sub>, is an important parameter to consider in parallel data applications where synchronization of signals on parallel data lines is a concern.

If the parallel data is being sent through a group of optocouplers, differences in propagation delays cause the data to arrive at the outputs of the optocouplers at different times. If this difference in propagation delays is large enough, it determines the maximum rate at which parallel data can be sent through the optocouplers.

Propagation delay skew is defined as the difference between the minimum and maximum propagation delays, either  $t_{PLH}$  or  $t_{PHL}$ , for any given group of optocouplers which are operating

Figure 9 Propagation Delay Skew Waveform

under the same conditions (i.e., the same supply voltage, output load, and operating temperature). As shown in Figure 10, if the inputs of a group of optocouplers are switched either ON or OFF at the same time,  $t_{PSK}$  is the difference between the shortest propagation delay, either  $t_{PLH}$  or  $t_{PHL}$ , and the longest propagation delay, either  $t_{PLH}$  or  $t_{PHL}$ . As mentioned earlier,  $t_{PSK}$  can determine the maximum parallel data transmission rate.

Figure 10 is the timing diagram of a typical parallel data application with both the clock and the data lines being sent through optocouplers. The figure shows data and clock signals at the inputs and outputs of the optocouplers. To obtain the maximum data transmission rate, both edges of the clock signal are being used to clock the data; if only one edge were used, the clock signal would need to be twice as fast.

Propagation delay skew represents the uncertainty of where an edge might be after being sent through an optocoupler.

Figure 10 shows that there will be uncertainty in both the data and the clock lines. It is important that these two areas of uncertainty not overlap. Otherwise the clock signal might arrive before all of the data outputs have settled, or some of the data outputs might start to change before the clock signal has arrived.

From these considerations, the absolute minimum pulse width that can be sent through optocouplers in a parallel application is twice  $t_{PSK}$ . A cautious design should use a slightly longer pulse width to ensure that any additional uncertainty in the rest of the circuit does not cause a problem.

The t<sub>PSK</sub> specified optocouplers offer the advantages of guaranteed specifications for propagation delays, pulse-width distortion, and propagation delay skew over the recommended temperature and power supply ranges.

Figure 10 Parallel Data Transmission Example

### **Optocoupler CMR Performance**

The principal protection against common-mode noise comes from the fundamental isolation properties of the optocoupler, and this in turn is directly related to the Input-Output leakage capacitance of the optocoupler.

To provide maximum protection to circuitry connected to the input or output of the optocoupler, the leakage capacitance is minimized by having large separation distances at all points in the optocoupler construction, including the LED/photodiode interface.

In addition to the optocouplers' basic physical construction, additional circuit design steps mitigate the effects of common-mode noise. The most important of these is the Faraday shield on the photodetector stage.

A Faraday shield is effective in optocouplers because the internal modulation frequency (light) is many orders of magnitude higher than the common-mode noise frequency.

# Improving CMR Performance at the Application Level

In an end application, it is desirable that the optocouplers' common-mode isolation be as close as possible to that indicated in the data sheet specifications. The first step in meeting this goal is to ensure maximum separation between PCB interconnects on either side of the optocoupler is maintained and that PCB tracks beneath the optocoupler are avoided.

It is inevitable that a certain amount of CMR noise will be coupled into the inputs and this can potentially result in false-triggering of the input. This problem is frequently observed in devices with high input impedance. In some cases, this can cause momentary missing pulses and can even cause input circuitry to latch-up in some alternate technologies.

The ACPL-x6xL optocoupler family does not have an input latch-up issue. Even at very high CMR levels, such as those experienced in end equipment level tests (for example IEC61000-4-4), the ACPL-x6xL series is immune to latch-up because of the simple diode structure of the LED.

In some cases, achieving the rated data sheet CMR performance level is not possible in an application. This is often because of the practical requirement to actually connect the isolator input to the output of a dynamically changing signal rather than statically tying the input to  $V_{\rm DD}$  or GND.

To address achievable end application performance on data sheets, the ACPL-x6xL optocouplers include an additional typical performance specification for dynamic CMR in the electrical parameter table. The dynamic CMR specification indicates the typical achievable CMR performance as the input is toggled on or off during a CMR transient.

The logic output of the ACPL-x6xL optocouplers is mainly controlled by LED current level, and since the LED current features very fast rise and fall times, dynamic noise immunity is essentially the same as static noise immunity.

Despite their immunity to input latch-up and the excellent dynamic CMR immunity, ACPL-x6xL optocoupler devices are still potentially vulnerable to misoperation caused by turning the LED either on or off during a CMR disturbance. If the LED status could be ensured by design, the overall application level CMR performance would be that of the photodetector. To benefit from the inherently high CMR capabilities of the ACPL-x6xL family, take the following precautions when operating the LED at the application level.

In particular, ensure that the LED stays either on or off during a CMR transient. Some common design techniques to accomplish this include the following:

#### **Keep the LED On:**

Overdrive the LED with a higher-than-required forward current.

#### **Keep the LED Off:**

- 1. Reverse bias the LED during the off state.

- 2. Minimize the off-state impedance across the anode and cathode of the LED during the off state.

All of these methods allow the full CMR capability of the ACPL-x6xL family to be achieved, but they do have practical implementation issues or require a compromise on power consumption.

There is, however, an effective method to meet the goal of maintaining the LED status during a CMR event with no other design compromises other than a single added resistor.

This CMR optimization takes advantage of the differential connection to the LED. By ensuring the common-mode impedances at both the cathode and anode of the LED are equal, the CMR transient on the LED is effectively canceled. As shown in Figure 11, this is easily achieved by using two, instead of one, input bias resistors.

### **Split LED Bias Resistor for Optimum CMR**

Figure 11 shows the recommended drive circuit for the ACPL-x6xL that gives optimum common-mode rejection. The two current-setting resistors balance the common-mode impedances at the LED's anode and cathode. Common-mode transients can capacitively couple from the LED anode (or cathode) to the output-side ground causing current to be shunted away from the LED (which is not wanted when the LED should be on) or conversely causing current to be injected into the LED (which is not wanted when the LED should be off).

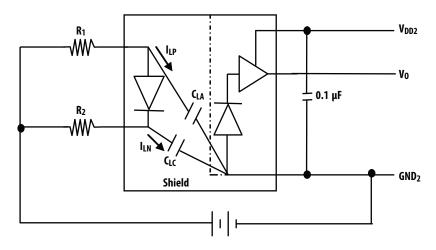

Figure 12 shows the parasitic capacitances ( $C_{LA}$  and  $C_{LC}$ ) between the LED's anode and cathode, and output ground. Also shown in Figure 12 on the input side is an AC-equivalent circuit.

Table 1 shows that the directions of  $I_{LP}$  and  $I_{LN}$  depend on the polarity of the common-mode transient. For transients occurring when the LED is on, common-mode rejection (CM<sub>L</sub>, since the output is at *low* state) depends on LED current ( $I_F$ ).

For conditions where  $I_F$  is close to the switching threshold ( $I_{TH}$ ), CM<sub>L</sub> also depends on the extent to which  $I_{LP}$  and  $I_{LN}$  balance each other. In other words, any condition where a common-mode transient causes a momentary decrease in  $I_F$  (meaning when  $dV_{CM}/dt > 0$  and  $|I_{FP}| > |I_{FN}|$ , referring to Table 1) also causes a common-mode failure for transients that are fast enough.

Likewise, for a common-mode transient that occurs when the LED is off (meaning CM<sub>H</sub>, since the output is at *high* state), if an imbalance between  $I_{LP}$  and  $I_{LN}$  results in a transient  $I_F$  equal to or greater than the switching threshold of the optocoupler, the transient signal can cause the output to spike below 2V, which constitutes a CM<sub>H</sub> failure.

The resistors recommended in Figure 11 include both the output impedance of the logic driver circuit and the external limiting resistor. The balanced  $I_{LED}$ -setting resistors help equalize the common-mode voltage change at the anode and cathode. This reduces  $I_{LED}$  changes caused by transient coupling through the parasitic capacitors  $C_{LA}$  and  $C_{LC}$  shown in Figure 12.

For ACPL-M61L/W61L:

$$V_{DD} = 3.3V$$

:  $R_1 = 510\Omega \pm 1\%$ ,  $R_2 = 360\Omega \pm 1\%$

$V_{DD} = 5.0V$ :  $R_1 = 1000\Omega \pm 1\%$ ,  $R_2 = 680\Omega \pm 1\%$

$R_T = R_1 + R_2$   $R_1/R_2 = 1.5$

For ACPL-064L/K64L:

$$\begin{split} &V_{DD} = 3.3V; R_1 = 430\Omega \pm 1\%, \, R_2 = 430\Omega \pm 1\% \\ &V_{DD} = 5.0V; \, R_1 = 845\Omega \pm 1\%, \, R_2 = 845\Omega \pm 1\% \\ &R_T = R_1 + R_2 \quad R_1/R_2 = 1 \end{split}$$

Figure 11 Recommended High-CMR Drive Circuit for the ACPL-x6xL

#### For ACPL-M61L/W61L:

$$\begin{split} V_{DD} &= 3.3V; \, R_1 = 510\Omega \pm 1\%, \, R_2 = 360\Omega \pm 1\% \\ V_{DD} &= 5.0V; \, R_1 = 1000\Omega \pm 1\%, \, R_2 = 680\Omega \pm 1\% \\ R_T &= R_1 + R_2 \quad R_1/R_2 = 1.5 \end{split}$$

#### For ACPL-064L/K64L:

$$\begin{split} V_{DD} &= 3.3V; \, R_1 = 430\Omega \pm 1\%, \, R_2 = 430\Omega \pm 1\% \\ V_{DD} &= 5.0V; \, R_1 = 845\Omega \pm 1\%, \, R_2 = 845\Omega \pm 1\% \\ R_T &= R_1 + R_2 \quad R_1/R_2 = 1 \end{split}$$

Figure 12 AC Equivalent Circuit of ACPL-x6xL

**Table 1 Common-Mode Pulse Polarity and LED Current Transient**

| dV <sub>CM</sub> /dt Value | Resultant I <sub>LP</sub> Flow<br>Direction     | Resultant I <sub>LN</sub> Flow<br>Direction       | If  I <sub>LP</sub>   <  I <sub>LN</sub>  , LED current I <sub>F</sub> is momentarily: | If $ I_{LP}  >  I_{LN} $ , LED current $I_F$ is momentarily: |

|----------------------------|-------------------------------------------------|---------------------------------------------------|----------------------------------------------------------------------------------------|--------------------------------------------------------------|

| Positive (> 0)             | Away from the LED anode through C <sub>LA</sub> | Away from the LED cathode through C <sub>LC</sub> | Increased                                                                              | Decreased                                                    |

| Negative (< 0)             | Toward the LED anode through C <sub>LA</sub>    | Toward the LED cathode through C <sub>LC</sub>    | Decreased                                                                              | Increased                                                    |

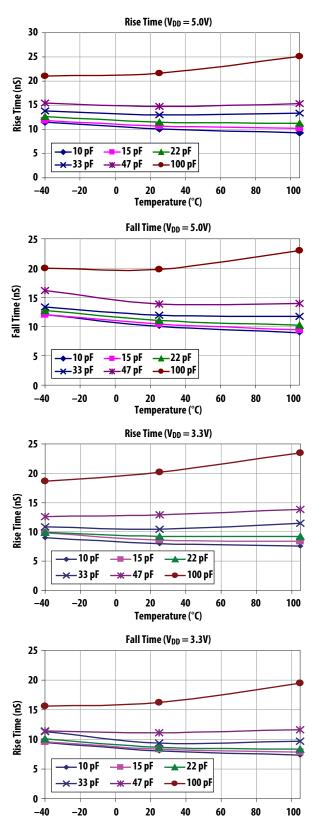

### **Slew-Rate Controlled Outputs Feature**

Typically, the output slew rate (rise and fall time) varies with the output load, as more time is required to charge up the higher load. The propagation delay and the PWD both increase with the load capacitance. This will be an issue especially in parallel communication because different communication lines will have different load capacitances. However, optocoupler ACPL-x6xL has a built-in slew-rate controlled feature to ensure that the output slew rate remains stable across wide load capacitance. Figure 13 shows the rise time and fall time for ACPL-x6xL at 3.3V and 5V.

Figure 13 Rise and Fall Time of ACPL-x6xL across Wide-Load Capacitance

Temperature (°C)

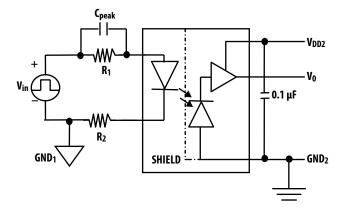

### **Speed Improvement**

A peaking capacitor can be placed across the input current-limit resistor (Figure 14) to achieve enhanced speed performance. The value of the peaking capacitor is dependent on the rise and fall time of the input signal, supply voltages, and LED input driving current ( $I_F$ ). Figure 15 shows significant improvement of propagation delay and pulse with distortion with an added peak capacitor at a driving current of 2 mA and 3.3V/5V power supply.

Figure 14 Connection of Peaking Capacitor ( $C_{peak}$ ) in Parallel with the Input Limiting Resistor ( $R_1$ ) to Improve Speed Performance

Figure 15 Improvement of t<sub>p</sub> and PWD with an Added 100-pF Peaking Capacitor in Parallel of Input Limiting Resistor

a.

$$V_{DD} = 5V$$

,  $C_{peak} = 47 \text{ pF}$ ,  $R_1 = 845\Omega$

b.

$$V_{DD} = 3.3V$$

,  $C_{peak} = 47 \text{ pF}$ ,  $R_1 = 430\Omega$

For product information and a complete list of distributors, please go to our web site: www.broadcom.com.

Broadcom, the pulse logo, Connecting everything, Avago Technologies, Avago, and the A logo are among the trademarks of Broadcom in the United States, certain other countries and/or the EU.

Copyright © 2016-2017 Broadcom. All Rights Reserved.

The term "Broadcom" refers to Broadcom Limited and/or its subsidiaries. For more information, please visit www.broadcom.com.

Broadcom reserves the right to make changes without further notice to any products or data herein to improve reliability, function, or design.

Information furnished by Broadcom is believed to be accurate and reliable. However, Broadcom does not assume any liability arising out of the application or use of this information, nor the application or use of any product or circuit described herein, neither does it convey any license under its patent rights nor the rights of others.

AV02-2150EN - October 6, 2017