## **R5436T Series**

## 3 to 5 Serial Cell Li-Ion or Li-Polymer Battery Protection IC

NO.EA-322-210618

#### **OUTLINE**

The R5436T is an overcharge, overdischarge and overcurrent protection IC for Li-ion or Li-polymer secondary battery. Overcharge, Overdischarge, Charge Overcurrent and Discharge Overcurrent for 3 to 5 serial cells can be detected. By cascade connection using the R5436T, it is also possible to protect 6-serial or more cells rechargeable battery pack. The R5436T provides a cell-balancing function to equalize imbalance between cells, and it provides an open-wire detection to detect a broken wire between a battery and the circuit board. The open-wire detection is optionally selectable.

#### **FEATURES**

|     | igh Voltage Tolerant Process                                          |                                                                                       |

|-----|-----------------------------------------------------------------------|---------------------------------------------------------------------------------------|

| Α   | bsolute Maximum Ratings ······                                        | · 30 V                                                                                |

|     | ow Supply Current                                                     |                                                                                       |

|     | Normal operation with using 5 cells ·····                             |                                                                                       |

|     | Standby ·····                                                         | · Typ. 6.0 µA                                                                         |

| • H | igh-accuracy Voltage Detection                                        |                                                                                       |

|     | Overcharge detection voltage (V <sub>DET1n</sub> (1)) ··············· | · 3.6 V to 4.5 V (in 5 mV steps)                                                      |

|     | Overcharge detection voltage accuracy·····                            |                                                                                       |

|     | Overdischarge detection voltage (V <sub>DET2n</sub> (1)) ···········  | · 2.0 V to 3.2 V (in 5 mV steps)                                                      |

|     | Overdischarge detection voltage accuracy ······                       | · ± 2.5%                                                                              |

|     | Discharge overcurrent detection voltage1(V <sub>DET31</sub> )(2)      | · 0.05 V to 0.25 V (in 10 mV steps)                                                   |

|     | Discharge overcurrent detection voltage accuracy ···                  | · Standard spec: ± 20mV                                                               |

|     |                                                                       | High standard spec (3): $\pm 15$ mV ( $V_{DET31} \le 0.15V$ ) /                       |

|     |                                                                       | $\pm 20 \text{ mV (V}_{DET31} > 0.15 \text{V})$                                       |

|     | Discharge overcurrent detection voltage2 (V <sub>DET32</sub> ) ···    | · V <sub>DET31</sub> × 3                                                              |

|     | Discharge overcurrent detection voltage2 accuracy                     | · Standard: ± 50mV                                                                    |

|     |                                                                       | High standard spec: ±25 mV(V <sub>DET31</sub> ≤ 0.10V) /                              |

|     |                                                                       | $\pm 50 \text{ mV}(V_{DET31} > 0.10V)$                                                |

|     | Short-circuit detection voltage <sup>(4)</sup> ······                 | 0.25 V to 1.0 V (in 20 mV steps)                                                      |

|     | Charge overcurrent detection voltage (V <sub>DET4</sub> )·········    |                                                                                       |

|     | Charge overcurrent detection voltage accuracy······                   | · Standard spec: ± 30 mV                                                              |

|     |                                                                       | High standard spec: $\pm 15 \text{ mV} (V_{DET4} = -0.05 \text{V} / -0.1 \text{V}) /$ |

|     |                                                                       | $\pm 30 \text{ mV } (V_{DET4} = -0.2 \text{V})$                                       |

|     | Overcharge release voltage······                                      | · V <sub>DET1n</sub> –0.1V to V <sub>DET1n</sub> –0.4V (in 10mV steps)                |

|     | Overdischarge release voltage ······                                  | $V_{DET2n}$ +0.0V to $V_{DET2n}$ +0.7V (in 50mV steps)                                |

|     |                                                                       | -provided, max.value is 3.2V.                                                         |

|     | Cell-balancing detection voltage (V <sub>CBDn</sub> (1))············  |                                                                                       |

|     | Cell-balancing release voltage ······                                 | · V <sub>CBDn</sub> –0.0V to V <sub>CBDn</sub> –0.4V (in 10mV steps)                  |

|     |                                                                       |                                                                                       |

$<sup>^{(1)}</sup>$  V<sub>DET1n</sub>, V<sub>CBDn</sub>: n = 1, 2, 3, 4, 5

<sup>(2)</sup> Set to meet the following equation: (3×V<sub>DET31</sub>+0.05<0.8×V<sub>SHORT</sub>).

$<sup>^{(3)}</sup>$  High standard spec: with improved accuracy for  $V_{DET31}$  /  $V_{DET32}$  /  $V_{DET4}$

$<sup>^{(4)}</sup>$   $V_{\text{DET}32}$  is not detected when  $V_{\text{DET}32}$  is higher than  $V_{\text{SHORT}}.$

### **APPLICATIONS**

■ Li-ion/Li-polymer battery protection for electric tool and electric bicycle, etc.

#### **SELECTION GUIDE**

In the R5436T, the set voltage, the delay time, and the optional function can be designated.

#### **Selection Guide**

| Product Name       | Package  | Quantity per Reel | Pb Free | Halogen Free |  |  |

|--------------------|----------|-------------------|---------|--------------|--|--|

| R5436Txxx*\$-E2-FF | TSSOP-28 | 3,000 pcs         | Yes     | Yes          |  |  |

xxx: Specify a combination of the following set voltages. Refer to Product Code List for details.

$V_{DET1n}$ <sup>(1)</sup>: 3.6 V to 4.5 V in 5 mV steps

$V_{\text{REL1n}}{}^{(1)}:V_{\text{DET1n}}\!-0.1~V$  to  $V_{\text{DET1n}}\!-0.4~V$  in 10 mV steps

V<sub>CBDn</sub><sup>(1)</sup>: 3.45 V to 4.45 V in 5mV steps

$V_{CBRn}^{(1)}$ :  $V_{CBDn} - 0.0 \text{ V}$  to  $V_{CBDn} - 0.4 \text{ V}$  in 10 mV steps

$V_{DET2n}^{(1)}$ : 2.0 V to 3.2 V in 5 mV steps

$V_{\text{REL2n}}\xspace^{(1)}$  :  $V_{\text{DET2n}}$  + 0.0 V to  $V_{\text{DET2n}}$  + 0.7 V in 50 mV steps (Max. 3.2 V)

$V_{\text{DET31}}$ : 0.05 V to 0.25 V in 10 mV steps

$V_{\text{DET}32}$  : Fixed to three times  $V_{\text{DET}31}$

V<sub>SHORT</sub>: 0.25 V to 1.0 V in 20 mV steps

V<sub>DET4</sub>: -0.05 V / -0.1V / -0.2V

#### \*: Specify a combination of the following each detection delay time.

| Code | t <sub>VDET1</sub> [s] | t <sub>VDET2</sub> [ms]    | t <sub>VDET31</sub> [ms]   | t <sub>VDET32</sub> [ms] | t <sub>VDET4</sub> [ms] | t <sub>short</sub> [µs] |

|------|------------------------|----------------------------|----------------------------|--------------------------|-------------------------|-------------------------|

| В    | 1.0                    | 3.60×C <sub>CT1</sub> [nF] | 3.00×C <sub>CT2</sub> [nF] | t <sub>VDET31</sub> /6   | 8                       | 330                     |

#### \$: Specify a combination of the optional functions.

| Code | Overcharge<br>Released Type | Overdischarge<br>Released Type | 0 V Charging | Open-wire<br>Detection |

|------|-----------------------------|--------------------------------|--------------|------------------------|

| Α    | Voltage Release             | Latch                          | Available    | Available              |

| В    | Voltage Release             | Voltage Release                | Available    | Unavailable            |

(1)  $V_{DET1n}$ ,  $V_{REL1n}$ ,  $V_{CBDn}$ ,  $V_{CBRn}$ ,  $V_{DET2n}$ ,  $V_{REL2n}$ : n = 1, 2, 3, 4, 5

#### **Product Code List**

The product code is determined by the combination of the set voltages (Overcharge Detection Voltage: VDET1n, Overcharge Release Voltage: V<sub>REL1n</sub>, Cell-balancing Detection Voltage: V<sub>CBDn</sub>, Cell-balancing Release Voltage: V<sub>CBRn</sub>, Overdischarge Detection Voltage: V<sub>DET2n</sub>, Overdischarge Release Voltage: V<sub>REL2n</sub>, Discharge Overcurrent Detection Voltage 1/2: VDET31 / VDET32, Short-circuit Detection Voltage: VSHORT, Charge Overcurrent Detection Voltage:  $V_{\text{DET4}}$ ), the delay time code, and the optional function code.

| Product Name                        |                    |                    |                   |                   | Set Vol            | tage (V)           |                    |                    |                    |                   |

|-------------------------------------|--------------------|--------------------|-------------------|-------------------|--------------------|--------------------|--------------------|--------------------|--------------------|-------------------|

| (Product Code)                      | V <sub>DET1n</sub> | V <sub>REL1n</sub> | V <sub>CBDn</sub> | V <sub>CBRn</sub> | V <sub>DET2n</sub> | V <sub>REL2n</sub> | V <sub>DET31</sub> | V <sub>DET32</sub> | V <sub>SHORT</sub> | V <sub>DET4</sub> |

| R5436T <b>401</b> BA                | 4.225              | 4.175              | 4.125             | 4.125             | 3.000              | 3.200              | 0.100              | 0.300              | 0.700              | -0.100            |

| R5436T <b>502</b> BA                | 4.250              | 4.100              | 4.200             | 4.190             | 2.500              | 3.000              | 0.100              | 0.300              | 0.420              | -0.050            |

| R5436T <b>502</b> BB                | 4.230              | 4.100              | 4.200             | 4.190             | 2.500              | 3.000              | 0.100              | 0.300              | 0.420              | -0.030            |

| R5436T <b>503</b> BA                | 4.250              | 4.150              | 4.200             | 4.190             | 2.800              | 3.200              | 0.100              | 0.300              | 0.420              | -0.050            |

| R5436T <b>503</b> BB                | 4.230              | 4.130              | 4.200             | 4.130             | 2.000              | 3.200              | 0.100              | 0.300              | 0.420              | -0.030            |

| R5436T <b>504</b> BA                | 4.280              | 4.220              | 4.180             | 4.170             | 2.500              | 3.000              | 0.100              | 0.300              | 0.420              | -0.050            |

| R5436T <b>504</b> BB                | 4.200              | 4.220              | 4.100             | 4.170             | 2.500              | 3.000              | 0.100              | 0.300              | 0.420              | -0.030            |

| R5436T <b>505</b> BA                | 3.800              | 3.500              | 3.550             | 3.540             | 2.200              | 2.500              | 0.080              | 0.240              | 0.300              | -0.050            |

| R5436T <b>505</b> BB <sup>(1)</sup> | 3.000              | 3.300              | 3.330             | 3.340             | 2.200              | 2.500              | 0.000              | 0.240              | 0.500              | -0.030            |

| R5436T <b>506</b> BA                | 3.800              | 3.600              | 3.600             | 3.550             | 2.750              | 3.000              | 0.150              | 0.450              | 0.450              | -0.050            |

| R5436T <b>506</b> BB <sup>(1)</sup> | 3.000              | 3.000              | 3.000             | 3.330             | 2.730              | 3.000              | 0.130              | 0.430              | 0.430              | -0.030            |

| R5436T <b>507</b> BA                | 4.200              | 4.170              | 4.160             | 4.150             | 2.800              | 3.000              | 0.100              | 0.300              | 0.420              | -0.050            |

| R5436T <b>508</b> BA                | 3.650              | 3.450              | 3.550             | 3.530             | 2.000              | 2.500              | 0.100              | 0.300              | 0.420              | -0.050            |

| R5436T <b>508</b> BB                | 3.030              | 3.430              | 3.330             | 3.330             | 2.000              | 2.500              | 0.100              | 0.300              | 0.420              | -0.030            |

| R5436T <b>509</b> BA                | 4.350              | 4.150              | 4.300             | 4.290             | 2.700              | 3.000              | 0.100              | 0.300              | 0.420              | -0.050            |

| R5436T <b>510</b> BA                | 4.250              | 4.100              | 4.225             | 4.215             | 2.500              | 3.000              | 0.100              | 0.300              | 0.420              | -0.050            |

| R5436T <b>511</b> BA                | 4.250              | 4.150              | 4.200             | 4.190             | 2.750              | 3.000              | 0.080              | 0.240              | 0.300              | -0.050            |

| R5436T <b>511</b> BB                | 4.230              | 4.130              | 4.200             | 4.190             | 2.750              | 3.000              | 0.060              | 0.240              | 0.300              | -0.050            |

| R5436T <b>513</b> BB                | 4.400              | 4.250              | 4.350             | 4.340             | 2.700              | 3.000              | 0.100              | 0.300              | 0.420              | -0.050            |

| R5436T <b>514</b> BB                | 4.250              | 4.150              | 4.200             | 4.190             | 2.150              | 2.250              | 0.250              | 0.750              | 1.000              | -0.200            |

| R5436T <b>515</b> BB                | 3.650              | 3.450              | 3.550             | 3.530             | 2.300              | 3.000              | 0.100              | 0.300              | 0.420              | -0.050            |

| R5436T <b>516</b> BA                | 4.180              | 4.150              | 4.160             | 4.150             | 2.750              | 2.850              | 0.100              | 0.300              | 0.420              | -0.050            |

| R5436T <b>517</b> BB                | 4.180              | 4.150              | 4.145             | 4.135             | 2.800              | 2.900              | 0.050              | 0.150              | 0.250              | -0.050            |

| R5436T <b>518</b> BB <sup>(1)</sup> | 3.650              | 3.500              | 3.450             | 3.440             | 2.300              | 2.500              | 0.050              | 0.150              | 0.250              | -0.050            |

| R5436T <b>519</b> BB <sup>(1)</sup> | 3.650              | 3.530              | 3.500             | 3.490             | 2.500              | 2.750              | 0.050              | 0.150              | 0.250              | -0.050            |

<sup>(1)</sup> High standard spec: with improved accuracy for V<sub>DET31</sub> / V<sub>DET32</sub> / V<sub>DET4</sub>, Refer to the Electrical Characteristics for details.

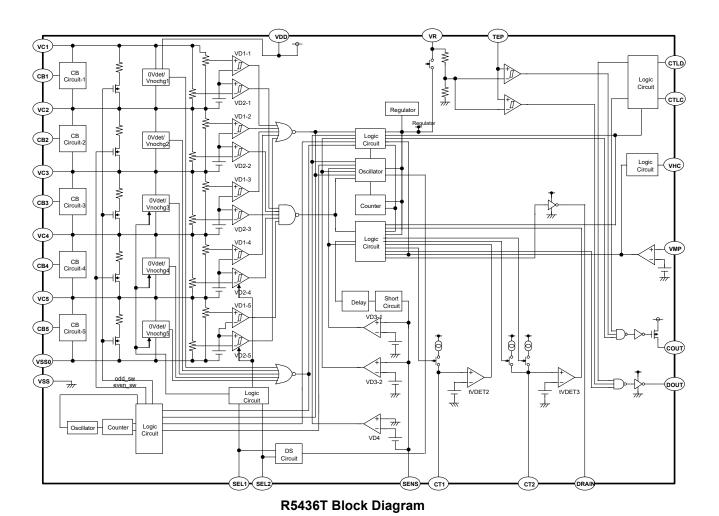

## **BLOCK DIAGRAM**

5

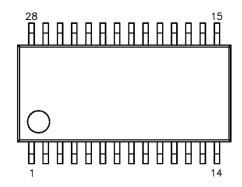

## **PIN DESCRIPTIONS**

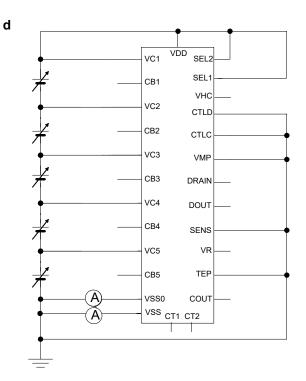

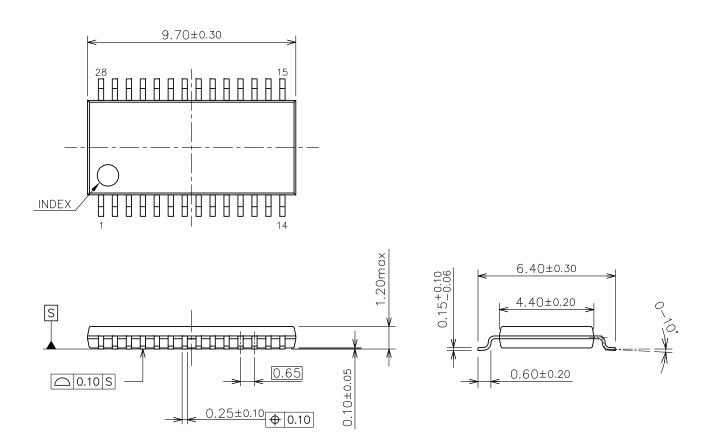

R5436T (TSSOP-28) Pin Configuration

#### **R5436T Pin Description**

| Pin No. | Symbol | Description                                                                 |

|---------|--------|-----------------------------------------------------------------------------|

| 1       | CTLC   | COUT control pin                                                            |

| 2       | CTLD   | DOUT control pin                                                            |

| 3       | COUT   | Overcharge detection output pin, Pch. open-drain output                     |

| 4       | VMP    | Charger negative input pin                                                  |

| 5       | DRAIN  | FET's gate connection pin for discharge overcurrent release voltage         |

| 6       | DOUT   | Overdischarge detection output pin, CMOS output                             |

| 7       | VHC    | Transmission pin for VMP input signal                                       |

| 8       | SENS   | Current sense pin                                                           |

| 9       | VR     | Internal VR output pin                                                      |

| 10      | TEP    | Temperature protection input pin                                            |

| 11      | VSS    | Ground pin for the IC                                                       |

| 12      | CT1    | Capacitor (C <sub>CT1</sub> ) connection pin for setting t <sub>VDET2</sub> |

| 13      | CT2    | Capacitor (C <sub>CT2</sub> ) connection pin for setting t <sub>VDET3</sub> |

| 14      | SEL1   | 3- / 4- / 5-cell selectable pins                                            |

| 15      | SEL2   | 3-74-75-ceil selectable piris                                               |

| 16      | VSS0   | Negative terminal for CELL5                                                 |

| 17      | CB5    | Cell balance control pin for CELL5                                          |

| 18      | VC5    | Positive terminal for CELL5                                                 |

| 19      | CB4    | Cell balance control pin for CELL4                                          |

| 20      | VC4    | Positive terminal for CELL4                                                 |

| 21      | CB3    | Cell balance control pin for CELL3                                          |

| 22      | VC3    | Positive terminal for CELL3                                                 |

| 23      | CB2    | Cell balance control pin for CELL2                                          |

| 24      | VC2    | Positive terminal for CELL2                                                 |

| 25      | CB1    | Cell balance control pin for CELL1                                          |

| 26      | NC     | No Connection                                                               |

| 27      | VC1    | Positive terminal for CELL1                                                 |

| 28      | VDD    | VDD pin                                                                     |

## **ABSOLUTE MAXIMUM RATINGS**

$(Ta = 25^{\circ}C, V_{SS} = 0 V)$

| Symbol            | Parameter                                | Rating                                       | Unit       |

|-------------------|------------------------------------------|----------------------------------------------|------------|

| V <sub>DD</sub>   | Supply voltage                           | -0.3 to 30                                   | V          |

| V <sub>C1</sub>   | CELL1 positive input pin voltage         | V <sub>C2</sub> -0.3 to V <sub>C2</sub> +6.5 | V          |

| $V_{C2}$          | CELL2 positive input pin voltage         | V <sub>C3</sub> −0.3 to V <sub>C3</sub> +6.5 | V          |

| $V_{C3}$          | CELL3 positive input pin voltage         | $V_{C4}$ -0.3 to $V_{C4}$ +6.5               | V          |

| $V_{C4}$          | CELL4 positive input pin voltage         | $V_{C5}$ -0.3 to $V_{C5}$ +6.5               | V          |

| $V_{C5}$          | CELL5 positive input pin voltage         | $V_{SS0}$ -0.3 to $V_{SS0}$ +6.5             | V          |

| $V_{\text{SS0}}$  | CELL5 negative input pin voltage         | -0.3 to V <sub>C5</sub> +0.3                 | V          |

| $V_{MP}$          | Charger negative input pin voltage       | $V_{DD}$ -30 to $V_{DD}$ +0.3                | V          |

| $V_{SEL1}$        | SEL1 pin input voltage                   | -0.3 to V <sub>DD</sub> +0.3                 | V          |

| $V_{\text{SEL2}}$ | SEL2 pin input voltage                   | -0.3 to V <sub>DD</sub> +0.3                 | V          |

| $V_{\text{CTLC}}$ | COUT control pin voltage                 | −0.3 to V <sub>DD</sub> +25 < 48             | V          |

| $V_{\text{CTLD}}$ | DOUT control pin voltage                 | -0.3 to V <sub>DD</sub> +25 < 48             | V          |

| $V_{SENS}$        | Current sense pin voltage                | $V_{VR}$ -6.5 to $V_{VR}$ +0.3               | V          |

| $V_{\text{CT1}}$  | Delay time setting 1 pin voltage         | -0.3 to V <sub>VR</sub> +0.3                 | V          |

| $V_{\text{CT2}}$  | Delay time setting 2 pin voltage         | -0.3 to V <sub>VR</sub> +0.3                 | V          |

| $V_{TEP}$         | Temperature protection input pin voltage | -0.3 to V <sub>VR</sub> +0.3                 | V          |

| Vсоит             | COUT pin output voltage                  | V <sub>DD</sub> -30 to V <sub>DD</sub> +0.3  | V          |

| $V_{DOUT}$        | DOUT pin output voltage                  | -0.3 to V <sub>OH2</sub> +0.3                | V          |

| VDRAIN            | DRAIN pin output voltage                 | -0.3 to V <sub>ОН3</sub> +0.3                | V          |

| $V_{\text{CB1}}$  | CB1 pin output voltage                   | V <sub>C2</sub> -0.3 to V <sub>C2</sub> +6.5 | V          |

| $V_{\text{CB2}}$  | CB2 pin output voltage                   | V <sub>C3</sub> -0.3 to V <sub>C3</sub> +6.5 | V          |

| $V_{CB3}$         | CB3 pin output voltage                   | V <sub>C4</sub> -0.3 to V <sub>C4</sub> +6.5 | V          |

| $V_{\text{CB4}}$  | CB4 pin output voltage                   | V <sub>C5</sub> -0.3 to V <sub>C5</sub> +6.5 | V          |

| $V_{CB5}$         | CB5 pin output voltage                   | -0.3 to 6.5                                  | V          |

| $V_{\text{VHC}}$  | VHC pin output voltage                   | $V_{DD}$ -3 to $V_{DD}$ +5                   | V          |

| $V_{\text{VR}}$   | VR pin output voltage                    | −0.3 to V <sub>VR</sub> +0.3                 | V          |

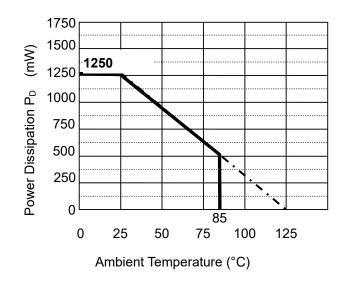

| P <sub>D</sub>    | Power Dissipation                        | Refer to Appendix "Power Di                  | ssipation" |

| Tj                | Junction Temperature Range               | -40 to 125                                   | °C         |

| Tstg              | Storage Temperature Range                | −55 to 125                                   | °C         |

#### ABSOLUTE MAXIMUM RATINGS

Electronic and mechanical stress momentarily exceeded absolute maximum ratings may cause permanent damage and may degrade the lifetime and safety for both device and system using the device in the field. The functional operation at or over these absolute maximum ratings is not assured.

#### RECOMMENDED OPERATING CONDITION

| Symbol   | Parameter                   | Rating    | Unit |

|----------|-----------------------------|-----------|------|

| $V_{DD}$ | Operating Input Voltage     | 2.5 to 25 | V    |

| Та       | Operating Temperature Range | -40 to 85 | °C   |

## RECOMMENDED OPERATING CONDITIONS

All of electronic equipment should be designed that the mounted semiconductor devices operate within the recommended operating conditions. The semiconductor devices cannot operate normally over the recommended operating conditions, even if they are used over such conditions by momentary electronic noise or surge. And the semiconductor devices may receive serious damage when they continue to operate over the recommended operating conditions.

### **ELECTRICAL CHARACTERISTICS**

$V_{CELLn}$  = CELLn (Ex.  $V_{CELL1}$  is a voltage difference between VC1 and VC2) n = 1, 2, 3, 4, 5, unless otherwise noted.

#### R5436TxxxBA / R5436TxxxBB Electrical Characteristics

(Ta = 25°C)

|                    |                                           |                                                                                       |                                                                                              |                               |                               |                                            | 1    | ,           |

|--------------------|-------------------------------------------|---------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|-------------------------------|-------------------------------|--------------------------------------------|------|-------------|

| Symbol             | Parameter                                 |                                                                                       | nditions                                                                                     | Min.                          | Тур.                          | Max.                                       | Unit | Circuit (1) |

| V <sub>DET1n</sub> | CELLn overcharge detection voltage        | voltage                                                                               | etection of supply                                                                           | V <sub>DET1n</sub><br>-0.025V | V <sub>DET1n</sub>            | V <sub>DET1n</sub><br>+0.025V              | V    | Α           |

| V <sub>REL1n</sub> | CELLn overcharge release voltage          | At falling edge d voltage                                                             | V <sub>REL1n</sub><br>-0.050V                                                                | V <sub>REL1n</sub>            | V <sub>REL1n</sub><br>+0.050V | V                                          | Α    |             |

| tvdet1             | Overcharge detection delay time           | $V_{CELL1}=3.5V \rightarrow 4$                                                        | <sub>Ln</sub> =3.5V (n=2,3,4,5)<br>1.5V                                                      | 0.7                           | 1.0                           | 1.3                                        | s    | В           |

| tvrel1             | Overcharge release delay time             | V <sub>CELL1</sub> =4.5V → 3                                                          | <sub>Ln</sub> =3.5V (n=2,3,4,5)<br>3.0V                                                      | 11                            | 16                            | 21                                         | ms   | В           |

| V <sub>CBDn</sub>  | CELLn cell balance detection voltage      | At rising edge de voltage                                                             | etection of supply                                                                           | V <sub>CBDn</sub><br>-0.025V  | $V_{CBDn}$                    | V <sub>CBDn</sub><br>+0.025V               | V    | С           |

| $V_{CBRn}$         | CELLn cell balance release voltage (2)    | voltage                                                                               | At falling edge detection of supply                                                          |                               |                               | VCBRn<br>+0.050V<br>or<br>VCBDn<br>+0.025V | V    | С           |

| t <sub>VCBD</sub>  | CELLn cell balance detection delay time   | V <sub>CELL1</sub> =3.5V → \                                                          | VDD=VC1,V <sub>CELLn</sub> =3.5V (n=2,3,4,5)<br>V <sub>CELL1</sub> =3.5V → V <sub>CBDn</sub> |                               |                               | 21                                         | ms   | С           |

| V <sub>DET2n</sub> | CELLn overdischarge detection voltage     | At falling edge d voltage                                                             | V <sub>DET2n</sub><br>x 0.975V                                                               | V <sub>DET2n</sub>            | V <sub>DET2n</sub><br>x1.025V | ٧                                          | D    |             |

| V <sub>REL2n</sub> | CELLn overdischarge release voltage       | At rising edge de voltage                                                             | V <sub>REL2n</sub><br>x 0.975V                                                               | V <sub>REN2n</sub>            | V <sub>REN2n</sub> x1.025V    | ٧                                          | D    |             |

| I <sub>CT1</sub>   | CT1 charging current                      | $V_{CELL1}=3.5V \rightarrow 2$                                                        | VDD=VC1,V <sub>CELLn</sub> =3.5V (n=2,3,4,5)<br>V <sub>CELL1</sub> =3.5V → 1.5V              |                               | 500                           | 650                                        | nA   | E           |

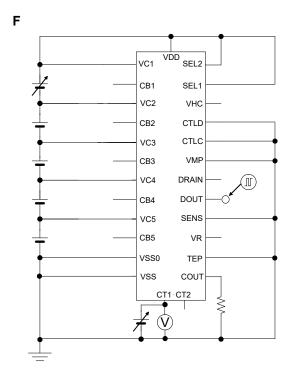

| V <sub>DCT1</sub>  | CT1 detection voltage                     | VDD=VC1,V <sub>CELL</sub><br>V <sub>CELL1</sub> =1.5V                                 | <sub>n</sub> =3.5V (n=2,3,4,5),                                                              | 1.44                          | 1.80                          | 2.16                                       | V    | F           |

| t <sub>VDET2</sub> | Overdischarge detection delay time        |                                                                                       | т <sub>1</sub> /I <sub>СТ1</sub> , С <sub>СТ1</sub> =3.3nF                                   | 83                            | 119                           | 155                                        | ms   | -           |

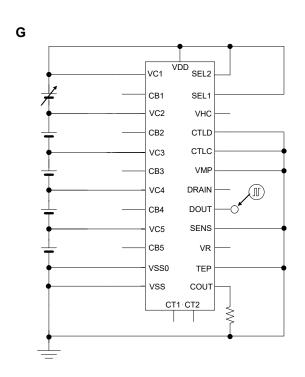

| t <sub>VREL2</sub> | Overdischarge release delay time          | VDD=VC1,V <sub>CELL</sub><br>V <sub>CELL1</sub> =1.5V → 3                             | n=3.5V (n=2,3,4,5)<br>3.5V                                                                   | 0.7                           | 1.2                           | 1.7                                        | ms   | G           |

|                    |                                           | VDD=VC1,                                                                              | Standard spec                                                                                | V <sub>DET31</sub><br>-0.020V |                               | V <sub>DET31</sub><br>+0.020V              |      |             |

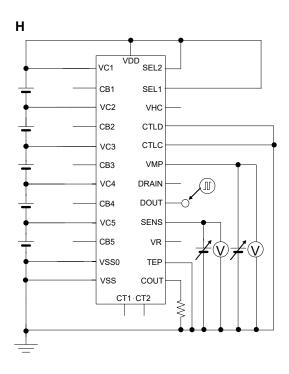

| V <sub>DET31</sub> | Discharge overcurrent detection voltage 1 | V <sub>CELLn</sub> =3.5V,<br>V <sub>MP</sub> =4.0V,<br>At rising edge<br>detection of | High standard spec V <sub>DET31</sub> ≤ 0.15V                                                | V <sub>DET31</sub><br>-0.015V | V <sub>DET31</sub>            | V <sub>DET31</sub><br>+0.015V              | ٧    | Н           |

|                    |                                           | SENS pin                                                                              | V <sub>DET31</sub> > 0.15V                                                                   | V <sub>DET31</sub><br>-0.020V |                               | V <sub>DET31</sub><br>+0.020V              |      |             |

|                    |                                           | VDD=VC1,                                                                              | Standard spec                                                                                | V <sub>DET32</sub><br>-0.050V |                               | V <sub>DET32</sub><br>+0.050V              |      |             |

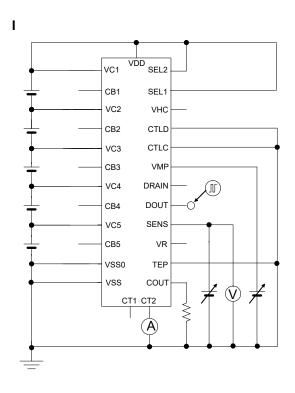

| V <sub>DET32</sub> | Discharge overcurrent detection voltage 2 | V <sub>CELLn</sub> =3.5V,<br>V <sub>MP</sub> =4.0V,<br>At rising edge<br>detection of | High standard spec V <sub>DET31</sub> ≤ 0.10V                                                | V <sub>DET32</sub>            | V <sub>DET32</sub>            | V <sub>DET32</sub><br>+0.025V              | V    | I           |

|                    |                                           | SENS pin V <sub>DETS</sub>                                                            |                                                                                              | V <sub>DET32</sub><br>-0.050V |                               | V <sub>DET32</sub><br>+0.050V              |      |             |

<sup>(1)</sup> Refer to TEST CIRCUITS for detail information.

$<sup>^{(2)}\,\</sup>text{Max.value}$  is equal to the lower value of  $V_{\text{CBRn}} + 0.050 V$  or  $V_{\text{CBDn}} + 0.025 V$ .

$V_{CELLn}$  = CELLn (Ex.  $V_{CELL1}$  is a voltage difference between VC1 and VC2) n = 1, 2, 3, 4, 5, unless otherwise noted.

## R5436TxxxBA / R5436TxxxBB Electrical Characteristics (Continued)

| Symbol              | Parameter                                    | Conditions                                                                              |                                                                             | Min.                                                | Тур.              | Max.                                                         | Unit | Circuit (1) |

|---------------------|----------------------------------------------|-----------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|-----------------------------------------------------|-------------------|--------------------------------------------------------------|------|-------------|

| V <sub>REL3</sub>   | Discharge overcurrent release voltage        |                                                                                         | etection of VMP pin                                                         | 0.8                                                 | 1.0               | 1.2                                                          | V    | Н           |

| I <sub>CT231</sub>  | CT2 charge current 1                         | VDD=VC1, V <sub>CEL</sub><br>SENS=V <sub>SS</sub> →0.4                                  | 350                                                                         | 500                                                 | 650               | nA                                                           | I    |             |

| I <sub>CT232</sub>  | CT2 charge current 2                         | VDD=VC1, V <sub>CEL</sub><br>SENS=V <sub>SS</sub> →0.7                                  |                                                                             | 2.0                                                 | 3.0               | 4.0                                                          | μA   | I           |

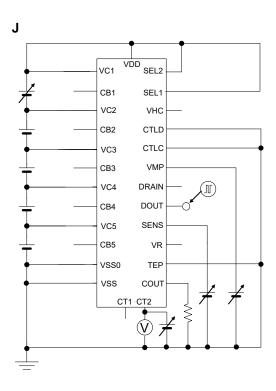

| V <sub>DCT2</sub>   | CT2 detection voltage                        | VDD=VC1, V <sub>CELI</sub><br>SENS=0.4V, VM                                             | P=4.0V                                                                      | 1.20                                                | 1.50              | 1.80                                                         | V    | J           |

| t <sub>VDET31</sub> | Discharge overcurrent detection delay time 1 | $t_{VDET31} = C_{CT2} \times V$<br>$C_{CT2} = 3.3 \text{nF}$                            |                                                                             | 6.9                                                 | 9.9               | 12.9                                                         | ms   | -           |

| tvdet32             | Discharge overcurrent detection delay time 2 | $t_{VDET32} = C_{CT2} \times V$<br>$C_{CT2} = 3.3 \text{nF}$                            | рст2/Іст232                                                                 | 1.1                                                 | 1.65              | 2.2                                                          | ms   | -           |

| t <sub>VREL3</sub>  | Discharge overcurrent release delay time     | V <sub>MP</sub> = 4.0V→V <sub>SS</sub>                                                  |                                                                             | 0.7                                                 | 1.2               | 1.7                                                          | ms   | Н           |

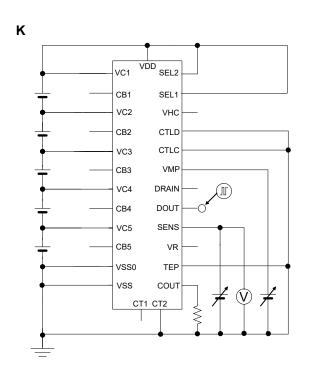

| V <sub>SHORT</sub>  | Short-circuit detection voltage              |                                                                                         | <sub>Ln</sub> =3.5V, V <sub>MP</sub> =4.0V,<br>etection of SENS pin         | V <sub>SHORT</sub> x 0.8                            | Vshort            | V <sub>SHORT</sub> x 1.2                                     | V    | K           |

| tshort              | Short-circuit detection delay time           | •                                                                                       | VDD=VC1, V <sub>CELLn</sub> =3.5V,<br>SENS=0.0V→2.0V, V <sub>MP</sub> =4.0V |                                                     | 330               | 430                                                          | μs   | К           |

|                     |                                              | VDD=VC1,                                                                                | Standard spec                                                               | V <sub>DET4</sub><br>-0.030V                        |                   | V <sub>DET4</sub><br>+0.030V                                 |      |             |

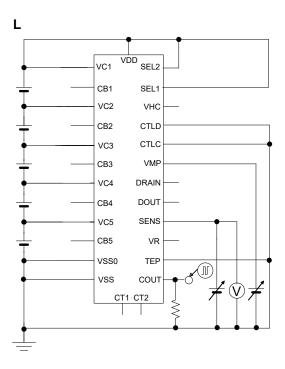

| V <sub>DET4</sub>   | Charge overcurrent detection voltage         | VCELLn=3.5V,<br>V <sub>MP</sub> = -1.0V,<br>At falling edge<br>detection of<br>SENS pin | High standard spec $V_{DET4} \ge -0.1V$ $V_{DET4} < -0.1V$                  | V <sub>DET4</sub> -0.015V V <sub>DET4</sub> -0.030V | V <sub>DET4</sub> | V <sub>DET4</sub><br>+0.015V<br>V <sub>DET4</sub><br>+0.030V | V    | L           |

| V <sub>REL4</sub>   | Charge overcurrent release voltage           | VDD=VC1, V <sub>CELI</sub>                                                              | Ln=3.5V<br>etection of VMP pin                                              | 0.05                                                | 0.1               | 0.15                                                         | V    | L           |

| t <sub>VDET4</sub>  | Charge overcurrent detection delay time      | VDD=VC1, V <sub>CEL</sub><br>SENS=0.0V→-1                                               | <sub>Ln</sub> =3.5V,                                                        | 5                                                   | 8                 | 11                                                           | ms   | L           |

| t <sub>VREL4</sub>  | Charge overcurrent release delay time        | VDD=VC1, V <sub>CELI</sub><br>V <sub>MP</sub> =-1.0V→1.0V                               | Ln =3.5V, SENS=V <sub>SS</sub> ,                                            | 0.7                                                 | 1.2               | 1.7                                                          | ms   | L           |

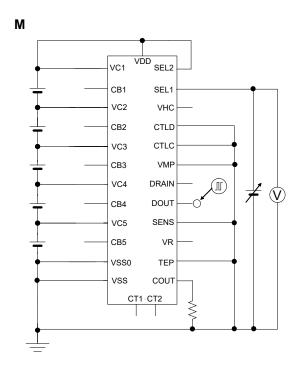

| V <sub>IH1</sub>    | SEL1 pin "High" input<br>voltage             | VDD=VC1, Vceli                                                                          | <sub>Ln</sub> =3.4V                                                         | V <sub>DD</sub> -<br>0.3V                           |                   | V <sub>DD</sub> +0.3V                                        | ٧    | М           |

| V <sub>IM1</sub>    | SEL1 pin "Middle" input voltage              | VDD=VC1, VCEL                                                                           | <sub>Ln</sub> =3.4V                                                         | 4.0                                                 |                   | V <sub>DD</sub> /2-0.5V                                      | V    | М           |

| V <sub>IL1</sub>    | SEL1 pin "Low" input voltage                 | VDD=VC1, V <sub>CELLn</sub> =3.4V                                                       |                                                                             | V <sub>SS</sub> -<br>0.3V                           |                   | V <sub>SS</sub> +0.3V                                        | ٧    | М           |

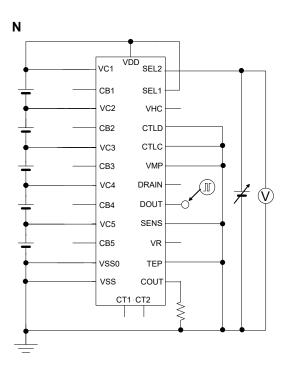

| V <sub>IH2</sub>    | SEL2 pin "High" input<br>voltage             | VDD=VC1, V <sub>CELLn</sub> =3.4V                                                       |                                                                             | V <sub>DD</sub> -<br>0.3V                           |                   | V <sub>DD</sub> +0.3V                                        | V    | N           |

| V <sub>IM2</sub>    | SEL2 pin "Middle" input voltage              | VDD=VC1, V <sub>CELI</sub>                                                              | <sub>Ln</sub> =3.4V                                                         | 4.0                                                 |                   | V <sub>DD</sub> /2-<br>0.5V                                  | V    | N           |

| V <sub>IL2</sub>    | SEL2 pin "Low" input voltage                 | VDD=VC1, V <sub>CEL</sub>                                                               | <sub>Ln</sub> =3.4V                                                         | V <sub>SS</sub> -<br>0.3V                           |                   | V <sub>SS</sub> +0.3V                                        | V    | N           |

<sup>(1)</sup> Refer to TEST CIRCUITS for detail information.

$V_{CELLn}$  = CELLn (Ex.  $V_{CELL1}$  is a voltage difference between VC1 and VC2) n = 1, 2, 3, 4, 5, unless otherwise noted.

## R5436TxxxBA / R5436TxxxBB Electrical Characteristics (Continued)

| Symbol                          | Parameter                              | Conditions                                                                                                                | Min.                    | Тур.                    | Max.                  | Unit | Circuit (1) |

|---------------------------------|----------------------------------------|---------------------------------------------------------------------------------------------------------------------------|-------------------------|-------------------------|-----------------------|------|-------------|

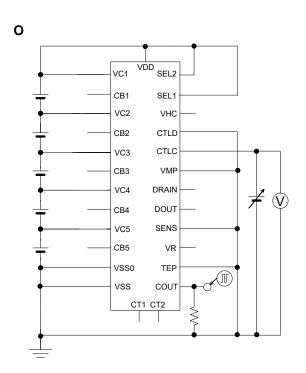

| V <sub>CTLC1H</sub>             | threshold voltage i                    | VDD=VC1, V <sub>CELLn</sub> =3.4V                                                                                         | 17.5                    | 18.1                    | 18.7                  | ٧    | 0           |

| V <sub>CTLC2H</sub>             | unconoid voltage z                     | VDD=VC1, V <sub>CELLn</sub> =3.4V                                                                                         | 15.1                    | 16.1                    | 16.6                  | ٧    | 0           |

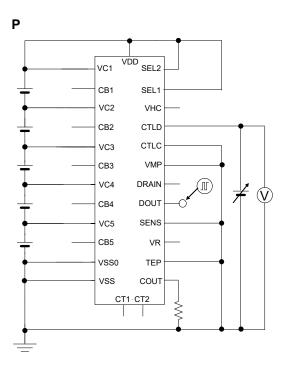

| V <sub>CTLD1H</sub>             | unoonoid voitago i                     | VDD=VC1, V <sub>CELLn</sub> =3.4V                                                                                         | 17.5                    | 18.1                    | 18.7                  | ٧    | Р           |

| V <sub>CTLD2H</sub>             | CTLD pin "High"<br>threshold voltage 2 | VDD=VC1, V <sub>CELLn</sub> =3.4V                                                                                         | 15.1                    | 16.1                    | 16.6                  | ٧    | Р           |

| t <sub>CTLD1</sub>              | CTLD pin input delay time 1            | VDD=VC1, V <sub>CELLn</sub> =3.4V<br>CTLD=V <sub>DD</sub> +0.5V→V <sub>DD</sub> +1.7V<br>R5436TxxxBB only                 |                         | 1.5                     | 6                     | ms   | Р           |

| t <sub>CTLD2</sub>              | CTLD pin input delay time 2            | VDD=VC1, V <sub>CELLn</sub> =3.4V<br>CTLD=V <sub>DD</sub> +1.7V→V <sub>DD</sub> +0.5V<br>R5436TxxxBB only                 |                         | 1.5                     | 6                     | ms   | Р           |

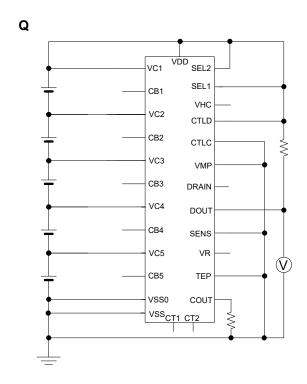

| $V_{\text{OL2}}$                | DOUT pin<br>Nch. ON voltage            | $I_{OL}$ =50 $\mu$ A, $V_{DD}$ = $V_{C1}$ , CTLD= $V_{DD}$<br>$V_{CELLn}$ =3.4 $V$                                        |                         | 0.1                     | 0.5                   | V    | Q           |

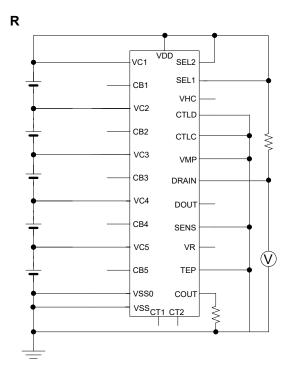

| V <sub>OL3</sub>                | DRAIN pin<br>Nch. ON voltage           | I <sub>OL</sub> =50μA, VDD=VC1, V <sub>CELLn</sub> =3.4V                                                                  |                         | 0.1                     | 0.5                   | ٧    | R           |

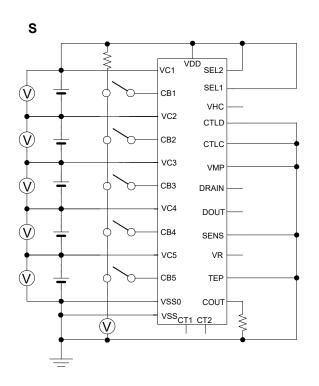

| V <sub>OL4</sub>                | CB1 pin<br>Nch. ON voltage             | $I_{OL}$ =50 $\mu$ A, VDD=VC1, $V_{CELLn}$ =3.4V                                                                          |                         | V <sub>C2</sub> +0.2V   | V <sub>C2</sub> +0.5V | ٧    | S           |

| V <sub>OL5</sub>                | CB2 pin<br>Nch. ON voltage             | I <sub>OL</sub> =50μA, VDD=VC1, V <sub>CELLn</sub> =3.4V                                                                  |                         | V <sub>C3</sub> +0.2V   | V <sub>C3</sub> +0.5V | ٧    | S           |

| V <sub>OL6</sub>                | CB3 pin<br>Nch. ON voltage             | I <sub>OL</sub> =50μA, VDD=VC1, V <sub>CELLn</sub> =3.4V                                                                  |                         | V <sub>C4</sub> +0.2V   | V <sub>C4</sub> +0.5V | ٧    | S           |

| V <sub>OL7</sub>                | CB4 pin<br>Nch. ON voltage             | I <sub>OL</sub> =50μA, VDD=VC1, V <sub>CELLn</sub> =3.4V                                                                  |                         | V <sub>C5</sub> +0.2V   | V <sub>C5</sub> +0.5V | ٧    | S           |

| V <sub>OL8</sub>                | CB5 pin<br>Nch. ON voltage             | I <sub>OL</sub> =50μA, VDD=VC1, V <sub>CELLn</sub> =3.4V                                                                  |                         | 0.2V                    | 0.5V                  | ٧    | S           |

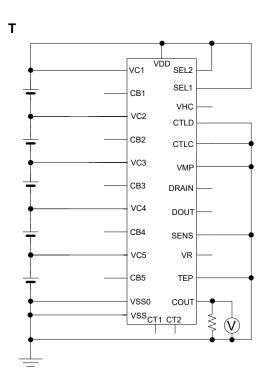

| V <sub>OH1</sub>                | COUT pin<br>Pch. ON voltage            | I <sub>OH</sub> =-50µA, VDD=VC1, CTLC=V <sub>SS</sub> , V <sub>CELLn</sub> =3.4V                                          | V <sub>DD</sub> -0.5V   | V <sub>DD</sub> -0.1V   |                       | ٧    | Т           |

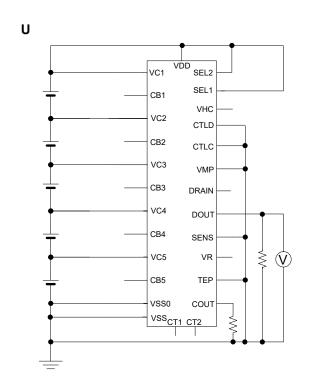

| $V_{\text{VR12}}$               | VR12V output voltage                   | $I_{OH}$ =-5 $\mu$ A, VDD=VC1,CTLD= $V_{SS}$ $V_{CELLn}$ =3.4 $V$ The measured value by pulling current through DOUT pin. | 9.5                     | 12                      | 14                    | V    | U           |

| V <sub>OH2</sub> <sup>(2)</sup> | DOUT pin<br>Pch. ON voltage            | I <sub>OH</sub> = -50μA, VDD=VC1,<br>CTLD= V <sub>SS</sub> , V <sub>CELLn</sub> =3.2V                                     | V <sub>VR12</sub> -0.5V | V <sub>VR12</sub> -0.1V |                       | ٧    | U           |

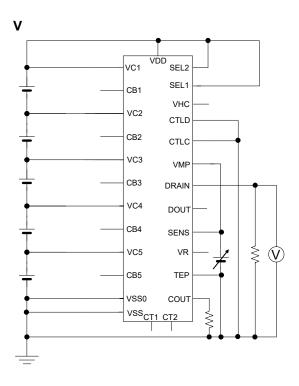

| V <sub>OH3</sub> <sup>(2)</sup> | DRAIN pin<br>Pch. ON voltage           | I <sub>OH</sub> = -50μA, VDD=VC1,<br>V <sub>CELL</sub> = 3.2V, SENS=VMP=4.0V                                              | V <sub>VR12</sub> -0.5V | V <sub>VR12</sub> -0.1V |                       | ٧    | V           |

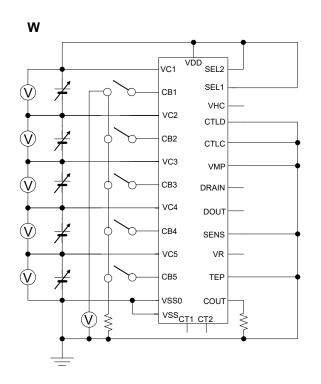

| V <sub>OH4</sub>                | CB1 pin Pch. ON voltage                | I <sub>OH</sub> = -50µA, VDD=VC1,V <sub>C1</sub> =4.5V,<br>V <sub>CELLn</sub> =3.2V(n=2,3,4,5)                            | V <sub>C1</sub> -0.5V   | V <sub>C1</sub> -0.3V   |                       | ٧    | W           |

| V <sub>OH5</sub>                | CB2 pin Pch. ON voltage                | I <sub>OH</sub> = -50µA, VDD=VC1,V <sub>C2</sub> =4.5V,<br>V <sub>CELLn</sub> =3.2V (n=1,3,4,5)                           | V <sub>C2</sub> -0.5V   | Vc2-0.3V                |                       | ٧    | W           |

| V <sub>OH6</sub>                | CB3 pin Pch. ON voltage                | I <sub>OH</sub> = -50μA, VDD=VC1,V <sub>C3</sub> =4.5V,<br>V <sub>CELLn</sub> =3.2V (n=1,2,4,5)                           | Vc3-0.5V                | Vc3-0.3V                |                       | V    | W           |

<sup>(1)</sup> Refer to TEST CIRCUITS for detail information.

$<sup>^{(2)}</sup>$  When  $V_{DD}$  <  $V_{VR12}$ -0.1V, DOUT / DRAIN pin voltage ( $V_{OH2}/V_{OH3}$ ) becomes almost equal to  $V_{DD}$ .

$\label{eq:Vcelln} V_{\text{CELLn}} = \text{CELLn (Ex. V}_{\text{CELL1}} \text{ is a voltage difference between VC1 and VC2)} \\ n = 1, 2, 3, 4, 5, \text{ unless otherwise noted.}$

## R5436TxxxBA / R5436TxxxBB Characteristics (Continued)

| Symbol             | Parameter                                       | Conditions                                                                                       | Min.                         | Тур.                              | Max.                         | Unit | Circuit |

|--------------------|-------------------------------------------------|--------------------------------------------------------------------------------------------------|------------------------------|-----------------------------------|------------------------------|------|---------|

| V <sub>OH7</sub>   | CB4 pin Pch. ON voltage                         | I <sub>OH</sub> = -50µA, VDD=VC1,V <sub>C4</sub> =4.5V,<br>V <sub>CELLn</sub> =3.2V (n=1,2,3,5)  | V <sub>C4</sub> -0.5V        | V <sub>C4</sub> -0.3V             |                              | ٧    | W       |

| V <sub>OH8</sub>   | CB5 pin Pch. ON voltage                         | I <sub>OH</sub> = -50μA, VDD=VC1,V <sub>C5</sub> =4.5V,<br>V <sub>CELLn</sub> =3.2V (n=1,2,3,4)  | V <sub>C5</sub> -0.5V        | V <sub>C5</sub> -0.3V             |                              | ٧    | W       |

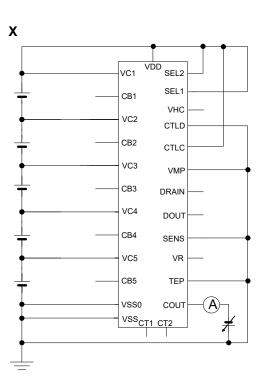

| I <sub>LCOUT</sub> | COUT pin off leakage-<br>current                | VDD=VC1, V <sub>CELLn</sub> =3.4V,C <sub>TLC</sub> =V <sub>DD</sub> ,<br>C <sub>OUT</sub> = -14V | -0.1                         |                                   |                              | μA   | Х       |

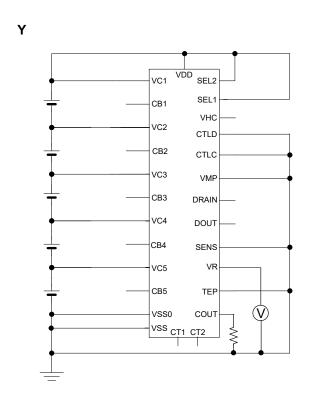

| $V_{VR}$           | VR output voltage                               | VDD=VC1, V <sub>CELLn</sub> =3.4V                                                                | 3.5                          | 3.6                               | 3.7                          | V    | Υ       |

| V <sub>T_DET</sub> | Detection voltage of TEP temperature protection | VDD=VC1, V <sub>CELLn</sub> =3.4V                                                                | V <sub>T_DET</sub><br>-0.027 | V <sub>T_DET</sub> <sup>(2)</sup> | V <sub>T_DET</sub><br>+0.035 | ٧    | Z       |

| V <sub>T_REL</sub> | Release voltage of TEP temperature protection   | VDD=VC1, V <sub>CELLn</sub> =3.4V                                                                | V <sub>T_REL</sub><br>-0.043 | V <sub>T_REL</sub> <sup>2</sup>   | V <sub>T_REL</sub><br>+0.050 | V    | Z       |

| t <sub>T_DET</sub> | TEP detection delay time                        | VDD=VC1, V <sub>CELLn</sub> =3.4V,<br>V <sub>TEP</sub> =0V→2V                                    | 5                            | 8                                 | 11                           | ms   | Z       |

| t <sub>T_REL</sub> | TEP release delay time                          | VDD=VC1, V <sub>CELLn</sub> =3.4V,<br>V <sub>TEP</sub> =2V→0V                                    | 11                           | 16                                | 21                           | ms   | Z       |

| t∟⊤                | Broken wire scanning cycle                      | VDD=VC1, V <sub>CELLn</sub> =V <sub>CBDn</sub> +0.05V                                            | 0.7                          | 1.25                              | 1.8                          | S    | а       |

| $V_{\text{HCO1}}$  | VHC pin<br>Nch. ON voltage 1                    | $I_{OH}$ = 2 $\mu$ A, VDD=VC1, V <sub>CELLn</sub> =3.4V, V <sub>MP</sub> =0V                     | 14.5                         | 15.5                              | 16.5                         | V    | С       |

| V <sub>HCO2</sub>  | VHC pin<br>Nch. ON voltage 2                    | $I_{OH}$ =10 $\mu$ A, VDD=VC1, V <sub>CELLn</sub> =3.4V, V <sub>MP</sub> =0V                     |                              | V <sub>HC1</sub> +0.3             | V <sub>HC1</sub> +0.5        | ٧    | С       |

| I <sub>LVHC</sub>  | VHC pin off leakage-<br>current                 | VDD=VC1, V <sub>CELLn</sub> =3.4V, V <sub>MP</sub> =0.5V, V <sub>HC</sub> =32V                   |                              |                                   | 0.1                          | μΑ   | b       |

| lss <sub>1</sub>   | Supply current 1                                | VDD=VC1, C <sub>OUT</sub> =OPEN<br>V <sub>CELLn</sub> =V <sub>DET1n</sub> - 0.4V                 |                              | 12                                | 30                           | μA   | d       |

| I <sub>SS2</sub>   | Supply current 2                                | VDD=VC1, C <sub>OUT</sub> =OPEN<br>V <sub>CELLn</sub> =1.5V                                      |                              | 6                                 | 12                           | μA   | d       |

| V <sub>STB</sub>   | Power ON voltage at standby mode                | VDD=VC1=1.5V, V <sub>CELLn</sub> =3.4V (n=2,3,4,5),<br>At rising edge detection of VMP pin       | 0.9                          | 1.13                              | 1.35                         | ٧    | Н       |

<sup>(1)</sup> Refer to TEST CIRCUITS for detail information.

$<sup>\</sup>overset{(2)}{\vee} V_{T\_DET} = 20/21*V_{VR}, \ V_{T\_REL} = 27/29*V_{VR} \ (V_{VR} : VR \ pin \ output \ voltage)$

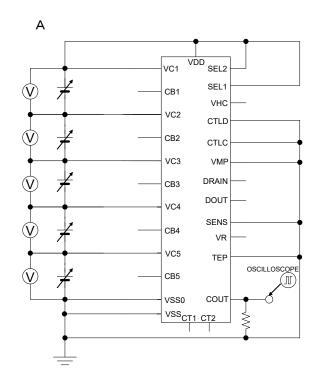

#### **TEST CIRCUITS**

#### THEORY OF OPERATION

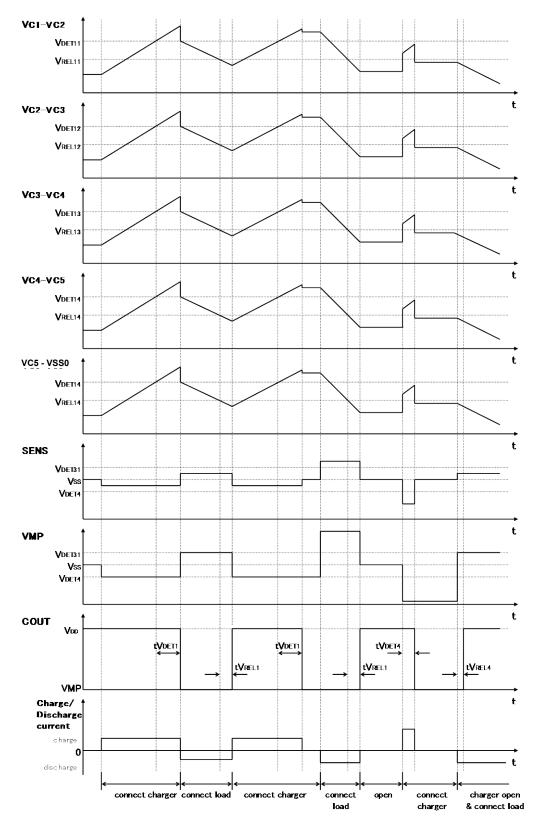

#### Overcharge Detection: VD1-n (n = 1, 2, 3, 4, 5)

During charging, the device supervises the voltage between VC1 and VC2 pins (the CELL1 voltage), the voltage between VC2 and VC3 pins (the CELL2 voltage), the voltage between VC3 and VC4 pins (the CELL3 voltage), the voltage between VC4 and VC5 pins (the CELL4 voltage), and the voltage between VC5 and VSS0 pins (the CELL5 voltage). If at least one of the cells' voltage becomes more than the overcharge detection voltage, the overcharge is detected, and COUT pin connected to an external pull-down resistor becomes "Hi-z", and it makes the external Nch.FET turn off. Then, the charging stops.

After detecting the overcharge, when all the cell voltage become lower than the overcharge detection voltage by connecting a load, COUT pin becomes "High", and it makes the external Nch. FET turn on, and the charging restarts. Even If all the cell voltage become lower than the overcharge release voltage with no load, COUT pin becomes "High" and the charging is available.

The device has internal fixed output delay times for overcharge detection and overcharge release. When the output delay time passes while any one of cell voltages is more than the overcharge detection voltage, the overcharge is detected. However, all cell voltage becomes lower than the overcharge detection voltage within the overcharge detection delay time, even if any one of cells' voltage becomes more than the overcharge detection voltage, the overcharge is not detected.

Besides, after detecting the overcharge, any one of their cell voltages becomes more than the overcharge release voltage within the overcharge release delay time, even if all the cell voltage becomes lower than the overcharge release voltage, the device does not release from the overcharge.

#### Overdischarge Detection: VD2-n (n = 1, 2, 3, 4, 5)

During discharging, the device supervises the voltage between VC1 and VC2 pins (the CELL1 voltage), the voltage between VC2 and VC3 pins (the CELL2 voltage), the voltage between VC3 and VC4 pins (the CELL3 voltage), the voltage between VC4 and VC5 pins (the CELL4 voltage), and the voltage between VC5 and VSS0 pins (the CELL5 voltage). If at least one of the cells' voltage becomes less than the overdischarge detection voltage, the overdischarge is detected, and DOUT pin becomes "Low", and it makes the external Nch.FET turn off. Then, the discharging stops.

The release condition from the overdischarge detection is different depending on optional functions. One is the latch type, after detecting the overdischarge, when the battery becomes higher than the overdischarge release voltage by connecting a charger, DOUT pin becomes "High". And, the other is the voltage release type, when the cell voltage becomes higher than the overdischarge release voltage, the device releases from the overdischarge even if the charger is not connected, and DOUT pin becomes "High".

An output delay time for overdischarge detection is settable by the external capacitor (C<sub>CT1</sub>) connected to CT1 pin. When the output delay time passes while any one of each cell voltage is lower than the overdischarge detection voltage, the overdischarge is detected. However, all cell voltage becomes higher than the overdischarge detection voltage within the overdischarge detection delay time even if any one of cells' voltage becomes lower than the overdischarge detection voltage, the overdischarge is not detected. An output delay time for overdischarge release is fixed internally.

After detecting the overdischarge, the device stops unnecessary circuits to reduce the consumption current to a minimum when VMP pin becomes "High". DOUT pin, which is CMOS output, outputs the internal regulator's voltage (about 12 V) at "High" level and outputs VSS pin voltage at "Low" level.

#### Discharge Overcurrent Detection: VD3-n (n = 1, 2) and Short-circuit Detection

During discharging, the device supervises SENS pin voltage (V<sub>SENS</sub>).

The discharge overcurrent is detected when SENS pin voltage (V<sub>SENS</sub>) becomes in between the discharge overcurrent detection voltage (V<sub>DET3n</sub>) and the short-circuit detection voltage (V<sub>SHORT</sub>) owing to a large load, and the short-circuit is detected when V<sub>SENS</sub> becomes more than V<sub>SHORT</sub>. Then, to prevent from flowing large current to circuits, DOUT pin is set to "Low" and the external FET is turned OFF.

The device has two detection threshold to detect the discharge overcurrent. Each detection threshold has the output delay time each other. The discharge overcurrent detection delay time 2 (tvDET32) is set to be shorter than the discharge overcurrent detection delay time 1 (tvDET31). An output delay time for discharge overcurrent detection is settable by the external capacitor (CcT2) connected to CT2 pin. When Vsens becomes lower than VDET3n within the output delay time even if Vsens is in between VDET3x and Vshort, the discharge overcurrent is not detected. The output delay times for discharge overcurrent release and short-circuit are fixed internally. Connect an external resistor for discharge overcurrent release among each drain of the external FETs connected to DRAIN, COUT, and DOUT pins. After detecting the discharge overcurrent, or the short-circuit, turn ON the external FET connected to DRAIN pin, and connect a resistor for overcurrent release to VSS. When load is released and opened after detecting the discharge overcurrent or the short-circuit, The VMP pin voltage (VvMP) is pulled-down to VSS via the resistor for the overcurrent release, and VvMP becomes less than VREL3. After a certain delay time, the discharge overcurrent detection state or the short-circuit detection state is released. When the discharge overcurrent detection is released, the external FET connected to DRAIN pin is turned OFF, and the resistor for the overcurrent release is disconnected from VSS.

#### **Charge Overcurrent Detection: VD4**

During charging or discharging, the device supervises SENS pin voltage (V<sub>SENS</sub>). When a large current flows by charging with an inappropriate charger, SENS pin voltage becomes less than the charge overcurrent detection voltage, and the charge overcurrent is detected. COUT pin with the external pull-down resistor becomes "Hi-z". And, tuning OFF the external FET can prevent from flowing large current to circuits.

When SENS pin voltage ( $V_{SENS}$ ) becomes higher than  $V_{DET4}$  within the output delay time even if  $V_{SENS}$  becomes lower than the charge overcurrent detection voltage, the charge overcurrent is not detected. The output delay times for charge overcurrent detection and charge overcurrent release are fixed internally.

To release from the charge overcurrent, connect a load without the charger, and VMP pin voltage has to become higher than the charge overcurrent release voltage over the charge overcurrent release delay time.

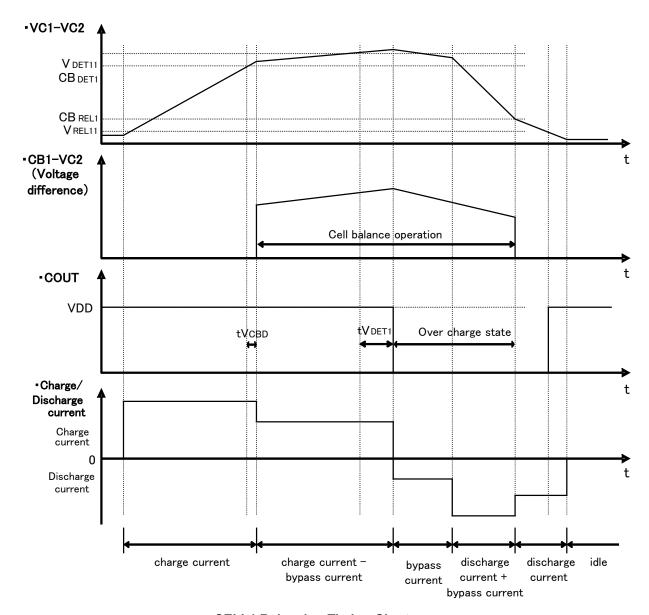

**Overcharge / Charge Overcurrent Operation Timing Chart**

Overdischarge / Discharge Overcurrent / Short-circuit Operation Timing Chart

#### **Standby Mode**

This device can change from normal mode to standby mode when overdischarge is detected and VMP pin voltage ( $V_{VMP}$ ) becomes higher than  $V_{STB}$ . In the standby mode, the device stops unnecessary circuits to reduce the consumption current to a minimum. At that time, VR pin output voltage becomes equal to the  $V_{SS}$  level. And, this device can return to the normal mode when  $V_{VMP}$  becomes lower than  $V_{STB}$  by connecting a charger.

#### Cell Imbalance

When any one of CELLs detects an overcharge and either one detects an overdischarge, COUT pin becomes "Hi-z" and DOUT pin becomes "Low".

#### **SEL1 and SEL2 Pins**

SEL1 and SEL2 pins are switching-control pins to select among 3- / 4- / 5-cell protection. When using for the 4-cell protection, connecting SEL1 pin to VSS and the SEL2 pin to VDD is required to stop the 5<sup>th</sup> cell protection circuit and shut signals. The overdischarge is not detected when VC5 pin is shortened to VSS0.

When using for the 3-cell protection, likewise, connecting SEL1 pin to VDD and SEL2 pin to VSS is required to stop the 5<sup>th</sup> and 4<sup>th</sup> cells protection circuits and shut signals. The overdischarge is not detected when VC4 and VC5 pins are shortened to VSS0. SEL1 / SEL2 pin must be fixed to VDD / VSS when using the 3- / 4- / 5-cell protection. Setting SEL1 and SEL2 pins can select disabling/enabling the open-wire detection<sup>(1)</sup> and the shorten mode 1/2. Refer to the following table for details of the operation mode.

#### **Operation Modes**

| Input Voltage <sup>(2)</sup> |          | Out and the Marks                                                        |

|------------------------------|----------|--------------------------------------------------------------------------|

| SEL1 Pin                     | SEL2 Pin | Operation Mode                                                           |

| High                         | High     | Enable the 5-cell protection mode                                        |

| Low                          | High     | Enable the 4-cell protection mode                                        |

| High                         | Low      | Enable the 3-cell protection mode                                        |

| Low                          | Low      | Disable the open-wire detection mode for 5-cell protection               |

| Low                          | Middle   | Disable the open-wire detection mode for 4-cell protection               |

| Middle                       | Low      | Disable the open-wire detection mode for 3-cell protection               |

| Middle                       | Middle   | Enable the delay time shorten mode 1 (approx.1/70) for 5-cell protection |

| Middle                       | High     | Enable the delay time shorten mode 2 (approx.4 ms) for 5-cell protection |

| High                         | Middle   | Enable the open-wire detecting test for 5-cell protection                |

<sup>(1)</sup> R5436TxxxBB does not support the open-wire detection.

<sup>(2) &</sup>quot;High": VDD level, "Middle": (VDD/2-0.5) V to (VDD-3) V, "Low": VSS level

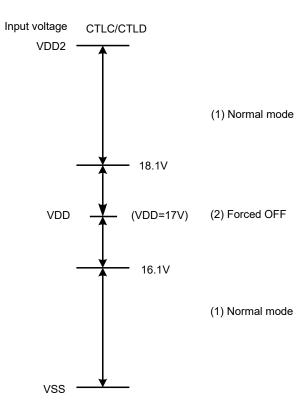

#### **CTLC and CTLD Pins**

When using cascade connection, the R5436T can transfer each state of overcharge, overdischarge, and openwire detections by connecting between COUT and CTLC pins and between DOUT and CTLD pins. When not using it, CTLC and CTLD pins must be connected to VSS.

When CTLC / CTLD pin voltage is higher than the value of "High" threshold voltage 1 (Vctlc1H / Vctld1H), or when CTLC / CTLD pin voltage is lower than the value of "High" threshold voltage 2 (Vctlc2H / Vctld2H), COUT / DOUT pin becomes "High" after normal operation. By applying a voltage of between Vctlc1H and Vctlc2H to CTLC pin, COUT pin with an external pull-down resistor becomes "Hi-z" forcedly. And, by applying a voltage of between Vctld1H and Vctld2H to CTLD pin, DOUT pin with an external pull-down resistor becomes "Low" forcedly. Don't make CTLC and CTLD pins open. The following table indicates a relationship between the control pins (CTLC and CTLD) and the state of the external FETs for COUT and DOUT pins.

#### External FET's state by CTLx pins

| CTLC / CTLD pins                       | External FET for COUT / DOUT pins |

|----------------------------------------|-----------------------------------|

| 2VDD to VCTLC1H / VCTLD1H              | ON (Normal operation)             |

| VCTLC1H / VCTLD1H to VCTLC2H / VCTLD2H | Forced OFF                        |

| Vss to Vctlc2H / Vctld2H               | ON (Normal operation)             |

When V<sub>DD</sub> = 17 V (Refer to "Electrical Characteristics"),

VCTLC1H / VCTLD1H: Typ.18.1 V VCTLC2H / VCTLD2H: Typ.16.1 V

#### CT1 and CT2 Pins

CT1 and CT2 pins are used for setting each output delay time of the overdischarge detection ( $t_{VDET2}$ ), and the discharge overcurrent detection 1/2 ( $t_{VDET31}$ /  $t_{VDET32}$ ) by connecting external capacitors  $C_{CT1}$  and  $C_{CT2}$ .  $t_{VDET2}$  can be set with CT1 pin.  $t_{VDET31}$  and  $t_{VDET32}$  can be set with CT2 pin. Each delay time can be calculated by following Equation 1:

CV = i\Delta t \cdots \cdots \cdots \cdot \cdot

■ Delay time (tvDET2) setting with external capacitor (CcT1) By substitution of Equation1,

t<sub>VDET2</sub> = C<sub>CT1</sub> x V<sub>DCT1</sub> / I<sub>CT1</sub> Equation 2

If  $C_{CT1} = 33$  nF,  $V_{DCT1} = 1.8$  V,  $I_{CT1} = 500$  nA (Refer to "Electrical Characteristics"). When substituting values to Equation 2,  $t_{VDET2}$  is as follow;

$$t_{VDET2}$$

= 33 nF x 1.8 V / 500 nA = 118.8 ms

■ Delay time (tvDET31, tvDET32) setting with external capacitor (CcT2) By substitution of Equation1,

```

t_{VDET31} = C_{CT2} \times V_{DCT2} / I_{CT2} Equation 3 t_{VDET32} = t_{VDET31} / 6 Equation 4

```

If  $C_{CT1} = 3.3$  nF,  $V_{DCT1} = 1.5$  V,  $I_{CT1} = 500$  nA (Refer to "Electrical Characteristics"). When substituting values to Equation 3 / Equation 4,  $t_{VDET31}$  and  $t_{VDET32}$  are as follow;

```

t_{VDET31} = 3.3 \text{ nF} \times 1.5 \text{ V} / 500 \text{ nA}

= 9.9 ms

t_{VDET32} = 9.9 \text{ ms} / 6

= 1.65 ms

```

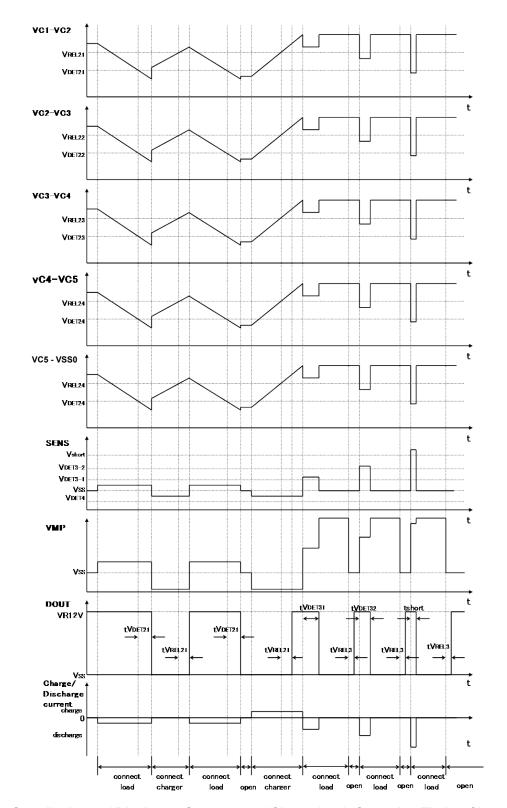

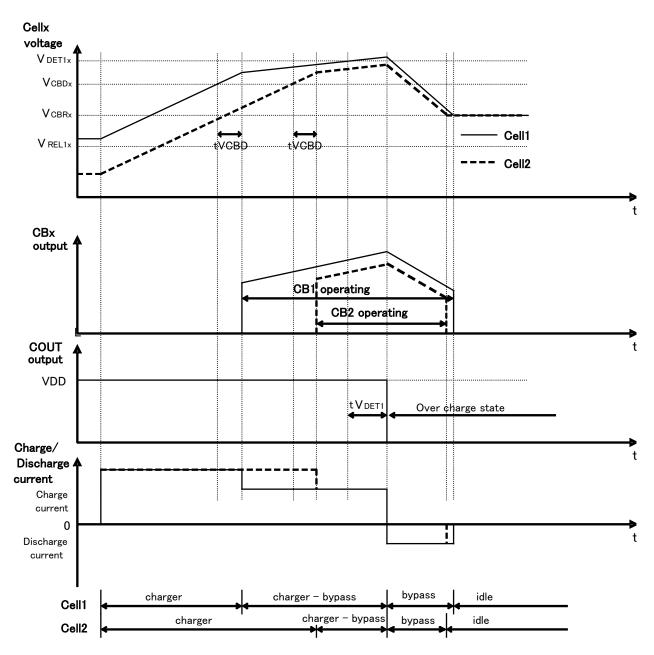

#### **Cell Balance Function**

When the cell voltage exceeds the cell balance detection voltage (V<sub>CBDn</sub>, n=1,2,3,4,5), CBn pin become "High" by cell balancing. By turning ON an external Nch. FET for cell balance, a current flows through the discharge path in parallel with the cell in order to reduce the charging current or to discharge the cell voltage. And, when the cell voltage is less than the cell balance release voltage (V<sub>CBRn</sub>, n=1,2,3,4,5), CBn pin become

"Low" after the cell balancing is released, and the external Nch. FET is turned OFF. When not using this function, CBn pin must be open.

**CELL1 Balancing Timing Chart**

**CELL1/2 Balancing Timing Chart**

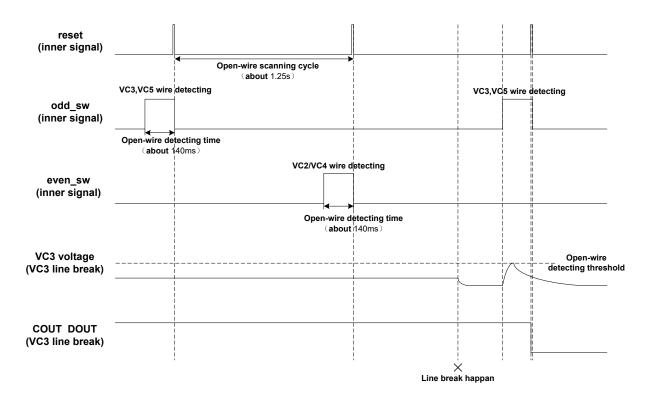

#### Open-wire Detection (R5436TxxxBA only)

When using the 5-cell protection, the voltage of VDD (= VC1) becomes lower than VC2 voltage if the connection between the battery and VDD (= VC1) is open. And, the voltage of VSS (= VSS0) becomes higher than VC5 voltage if the connection between the battery and VSS (= VSS0) is open. The voltage variation is detected as "Open-wire". When the open-wire is detected, COUT becomes "HI-z" and DOUT becomes "Low". But, if VC1 or VSS0 line is cut off when each VC1 and VSS0 pins are connected with separate lines, only DOUT pin will become "Low". Likewise, as for an open-wire detection between VDD and VSS pins, if VDD or VSS line is cut off, COUT pin will become "Hi-z" and DOUT pin will become "Low".

Open-wire detection for VC2, VC3, VC4, and VC5 is performed at interval of 1.25 seconds. The cell switch for VC1, VC3, and VC5 and the cell switch for VC2 and VC4 are alternately turned ON by even\_sw and odd\_sw signals. The internal impedance between pins, which are turned the switch ON, is lowered for about 140 ms. If not detecting the open-wire, this cycle will exit and the next cycle will start. If detecting the open-wire, the VC voltage will be shifted according to the difference of the internal impedance caused by turning ON either of two switches. This voltage change is detected during the delay time of 0.5 ms or more, the open-wire detection works. Then, COUT pin becomes "Hi-z" and DOUT pin becomes "Low". By applying a certain voltage to SEL1 and SEL2 pins, the open-wire detection for VC2, VC3, VC4, and VC5 is disabled. The open-wire detection is disabled even when this device is in standby mode - but the open-wire detection for VDD and VSS lines is enabled.

When using the 10-cell protection, if VSS of the higher-voltage device and VDD of the lower-voltage device in cascade connection are connected with the battery's line, an open-wire in this line cannot be detected.

#### [Limitations of Open-wire detection for VC2, VC3, VC4, and VC5]

When using the open-wire detection for VC2, VC3, VC4, and VC5, confirm the limitations below:

- The cycle time of open-wire detection is 1.25 second, and the open-wire detection is performed for 140

ms in each cycle. The device controls these internal-set times.

- When the battery voltage is lower even when this device is not in standby, an open-wire might not be

detected due to some factors: the device's distribution, the cell balancing in the battery, the operating

environment, the characteristics of the external components, etc.

- During the overcharge detection delay time, the device does not shift to the open-wire detection until the overcharge detection is finished. The overcharge detection does not start even if the battery voltage is higher than the overcharge detection voltage. After the completion of the open-wire detection, the overcharge detection will start if the battery voltage is more than the overcharge detection voltage. That is, the overcharge detection delay time increases for the time required for the open-wire detection.

- Likewise, the device does not shift to the open-wire detection during the overdisharge detection delay

time, and the device does not start the overdischarge detection when the battery voltage is less than the

overdischarge detection voltage during the open-wire detection. But, after the completion of the openwire detection, the overdischarge detection delay time increases for the time required for the open-wire

detection.

**Open-wire Detection Timing Chart**

#### **Temperature Protection by External NTC**

The temperature protection is realized with VR and TEP pins. VR pin supplies a source voltage to be divided by a series of resistors of R<sub>TEP</sub> and NTC. The divided voltage becomes an input to TEP pin.

When rising of the temperature under the NTC's supervising, TEP pin voltage, which is the divided voltage, rises depending on a reduction of the NTC resistance value. When the delay time  $(t_{T\_DET})$  has passed while holding the divided voltage being higher than the temperature protection detection voltage  $(V_{T\_DET})$ , the temperature protection will function, and changing COUT pin to "Hi-z" and DOUT pin to "Low" can stop charging/ discharging. After the temperature falling, the delay time  $(t_{T\_REL})$  has passed while holding the divided voltage being lower than the temperature protection release voltage  $(V_{T\_REL})$ , COUT and DOUT pins return "High", and charging / discharging is available.

VR pin cannot supply a large current because of supplying a source voltage for the voltage divider. In standby mode, the temperature protection stops since VR pin becomes "Low" to reduce the consumption current. When using the temperature protection at desired temperature, each resistance value of NTC and R<sub>TEP</sub> can be calculated by following Equation:

$$\frac{R_{TEP}}{R_{TEP} + R_{NTC}} \times VR = \frac{20}{21} \times VR$$

R<sub>TEP</sub> = 20 R<sub>NTC</sub>

For example, when using the following requirements:

NTC resistor: SNS104B24B24360FE1L050ET Available temperature for protection: 65°C

$R_{NTC} = 17.63 \text{ k}\Omega \text{ (at } 65^{\circ}\text{C)}$

Then,

R<sub>TEP</sub> =

$$20 \times R_{NTC}$$

=  $352.6 (k\Omega)$

As a result, choose a nearest value and normal type resistance:  $R_{TEP}$ =348K $\Omega$ .

#### **APPLICATION INFORMATION**

For battery pack assembly, it is recommended to start with the VSS connection, followed by the (+) terminal of the lowest cell in ascending voltage order.

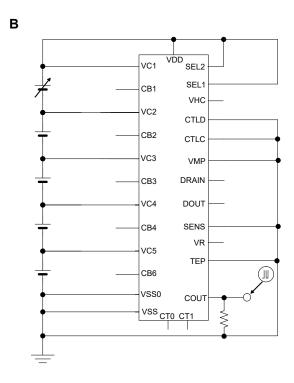

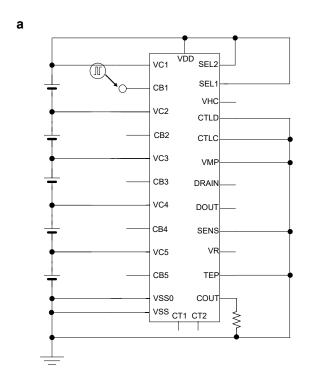

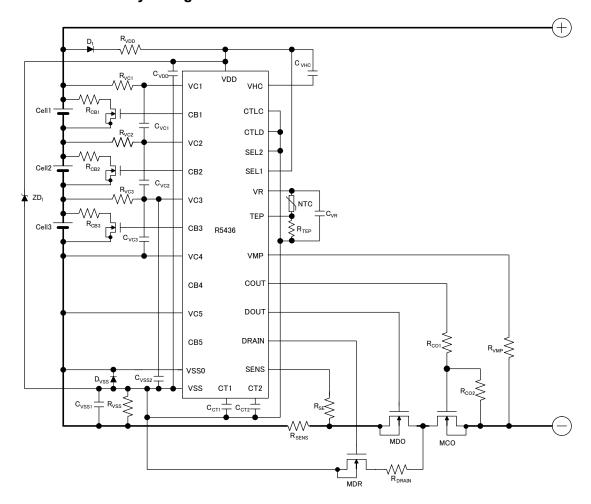

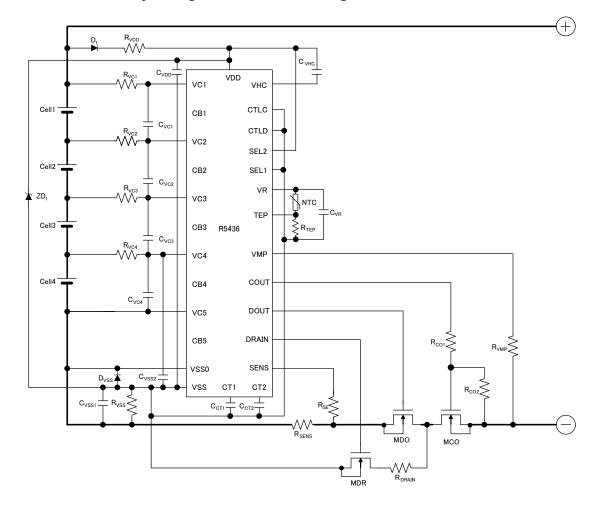

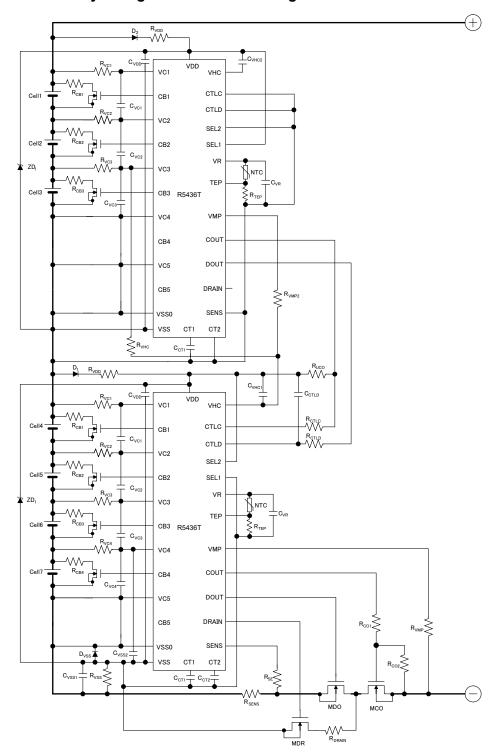

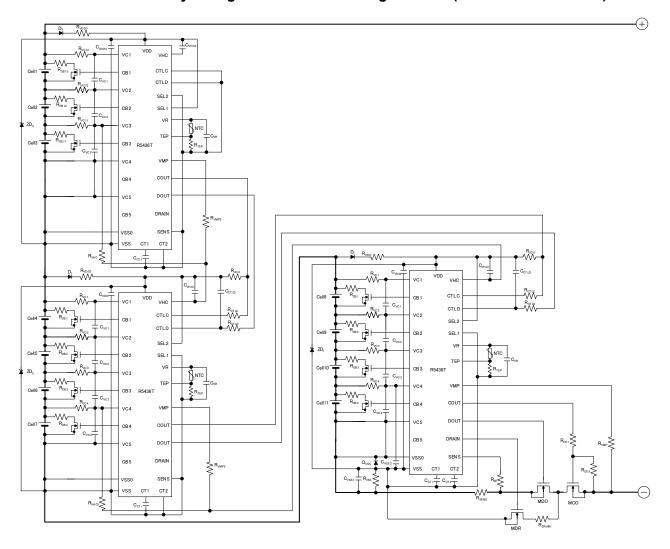

# Typical Application Circuits 1 3-cell Protection Battery Charger

Typical Application Circuit for 3-cell Protection Battery Charger

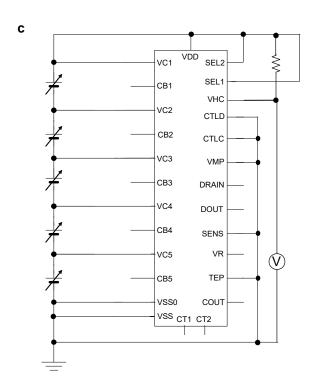

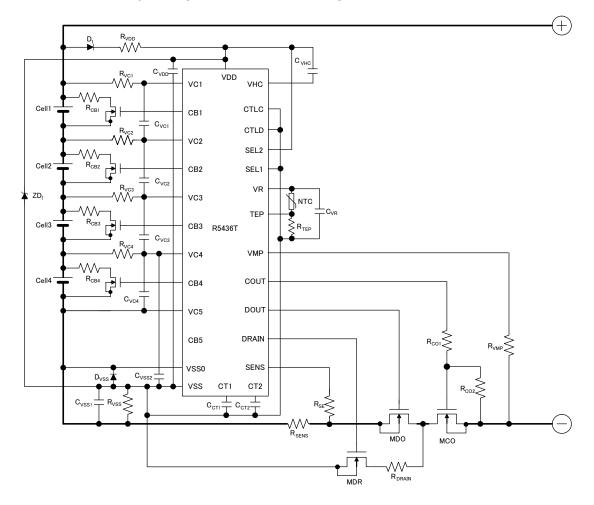

## **Typical Application Circuits 2**

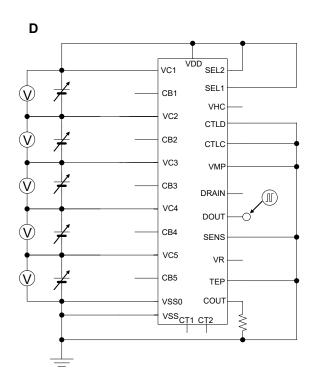

#### 4-cell Protection Battery Charger with Cell-balancing Disabled

Typical Application Circuit for 4-cell Protection Battery Charger with Cell-balancing Disabled

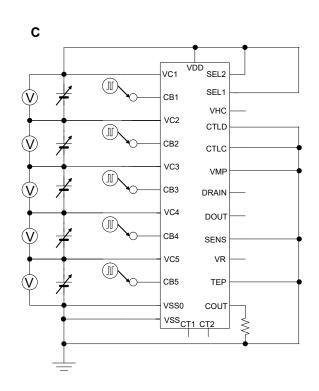

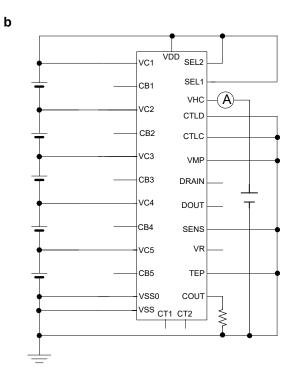

## 4-cell Protection Battery Charger with Cell-balancing Enabled

Typical Application Circuit for 4-cell Protection Battery Charger with Cell-balancing Enabled

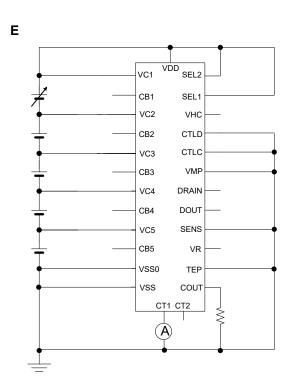

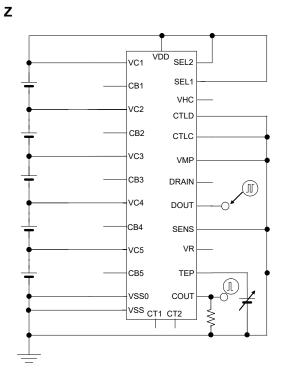

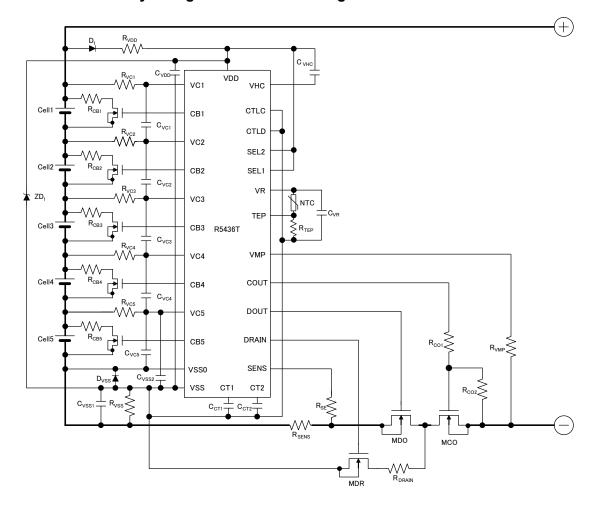

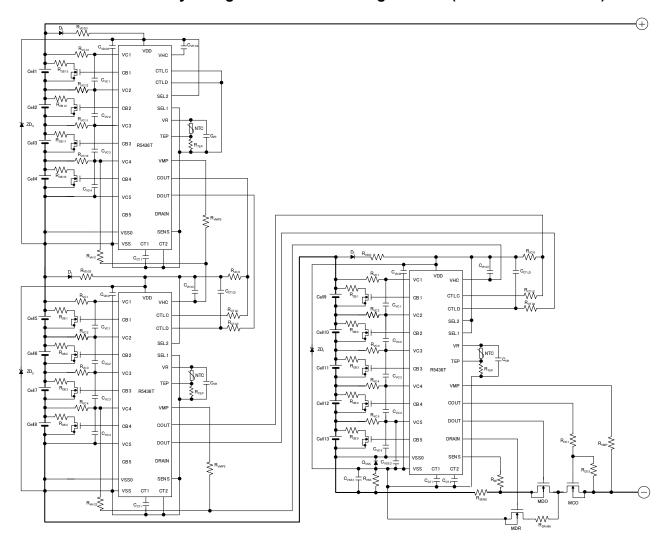

# Typical Application Circuits 3 5-cell Protection Battery Charger with Cell-balancing Enabled

Typical Application Circuit for 5-cell Protection Battery Charger with Cell-balancing Enabled

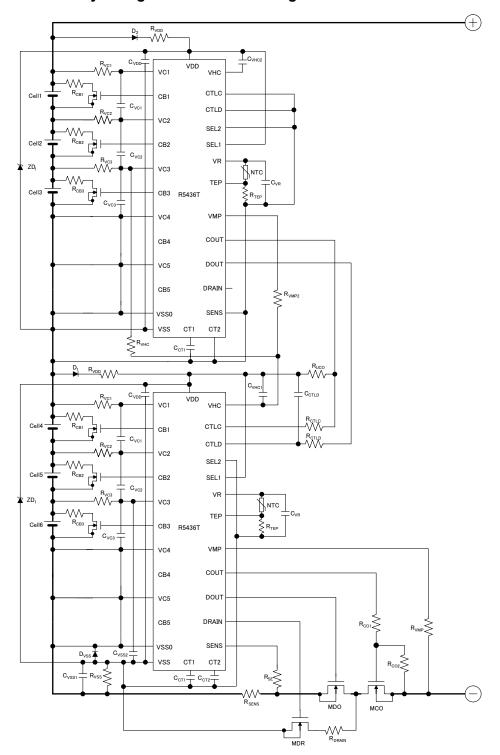

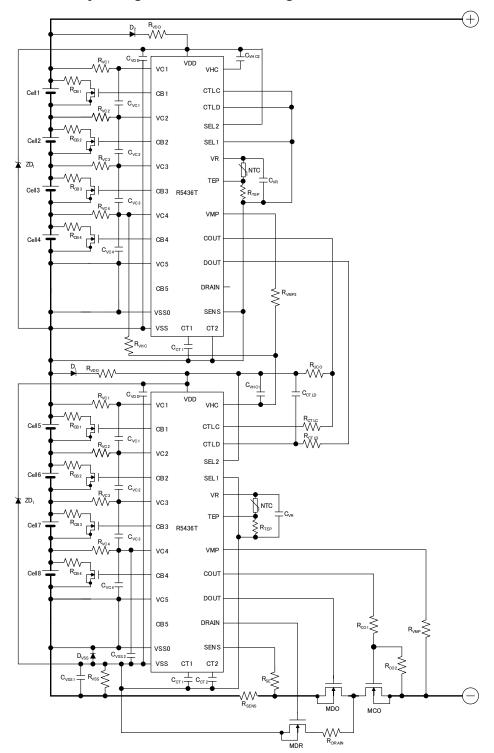

Typical Application Circuit for 6-cell Protection Battery Charger with Cell-balancing Enabled

Typical Application Circuit for 7-cell Protection Battery Charger with Cell-balancing Enabled

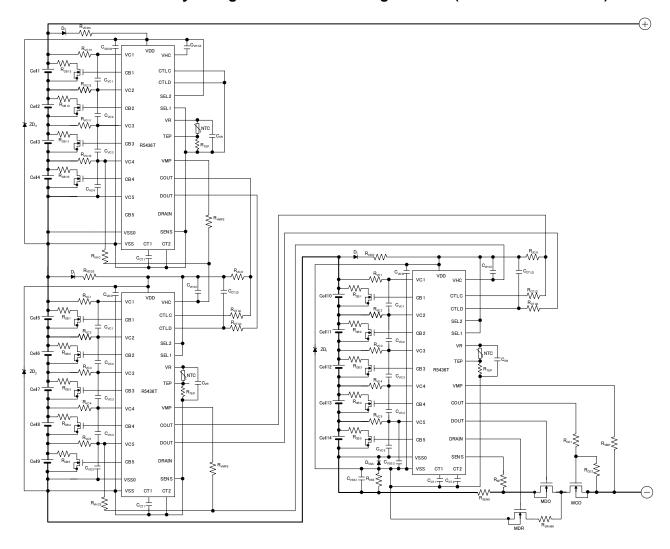

Typical Application Circuit for 8-cell Protection Battery Charger with Cell-balancing Enabled

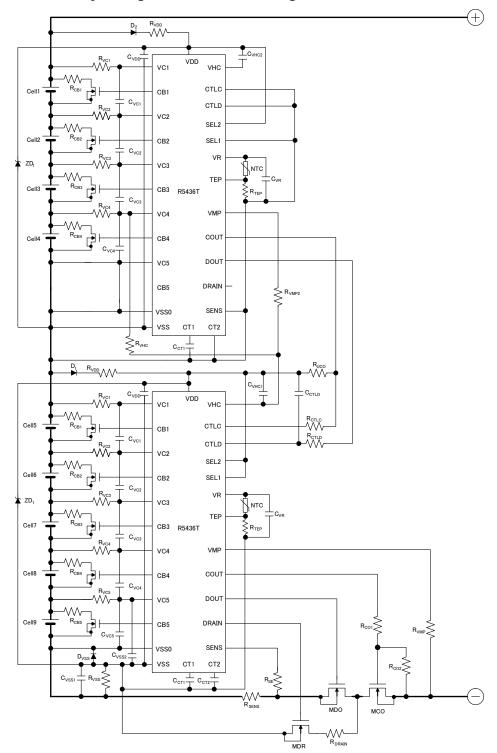

Typical Application Circuit for 9-cell Protection Battery Charger with Cell-balancing Enabled

Typical Application Circuit for 10-cell Protection Battery Charger with Cell-balancing Enabled

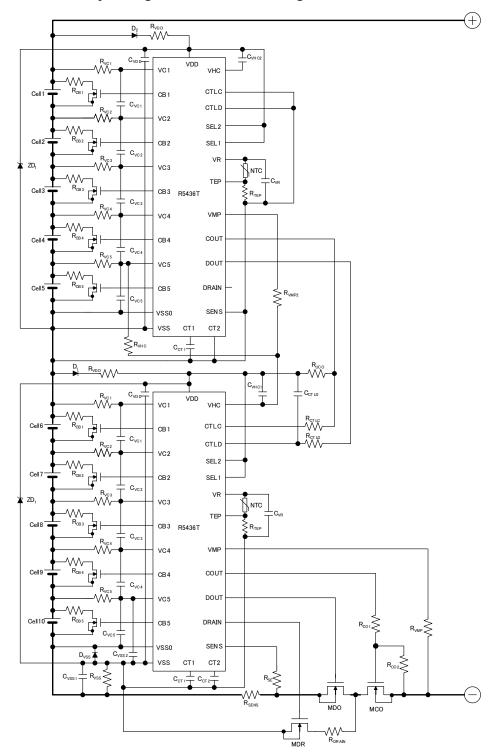

Typical Application Circuit for 11-cell Protection Battery Charger with Cell-balancing Enabled (Cascade Connection)

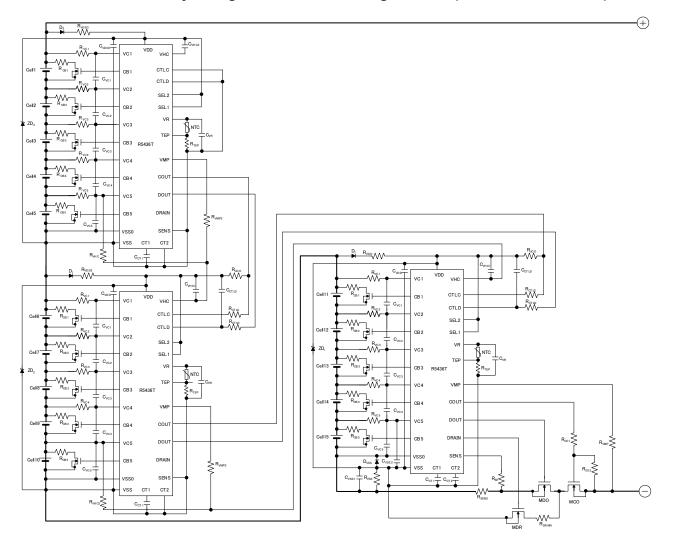

Typical Application Circuit for 12-cell Protection Battery Charger with Cell-balancing Enabled (Cascade Connection)

Typical Application Circuit for 13-cell Protection Battery Charger with Cell-balancing Enabled (Cascade Connection)

Typical Application Circuit for 14-cell Protection Battery Charger with Cell-balancing Enabled (Cascade Connection)

Typical Application Circuit for 15-cell Protection Battery Charger with Cell-balancing Enabled (Cascade Connection)

### **External Components**

| Symbol                               | Value (Typ.) | Range       | Unit | Remarks <sup>(1)</sup>                |

|--------------------------------------|--------------|-------------|------|---------------------------------------|

| R <sub>VDDX</sub>                    | 330          | 330 to 1000 | Ω    | Refer to Technical Note [1].          |

| R <sub>VC1X</sub>                    | 330          | 330 to 1000 | Ω    |                                       |

| R <sub>VC2X</sub>                    | 330          | 330 to 1000 | Ω    |                                       |

| R <sub>VC3X</sub>                    | 330          | 330 to 1000 | Ω    | Refer to Technical Note [2].          |

| R <sub>VC4X</sub>                    | 330          | 330 to 1000 | Ω    |                                       |

| R <sub>VC5X</sub>                    | 330          | 330 to 1000 | Ω    |                                       |

| R <sub>CB1X</sub>                    | 100          | Note [3]    | Ω    |                                       |

| R <sub>CB2X</sub>                    | 100          | Note [3]    | Ω    |                                       |

| R <sub>CB3X</sub>                    | 100          | Note [3]    | Ω    | Refer to Technical Note [3].          |

| R <sub>CB4X</sub>                    | 100          | Note [3]    | Ω    |                                       |

| R <sub>CB5X</sub>                    | 100          | Note [3]    | Ω    |                                       |

| Rsens                                | 100          | 1 or more   | mΩ   | Depending on Set Value of Overcurrent |

| RsE                                  | 10           | 1 to 10     | kΩ   | Refer to Technical Note [4].          |