TPS25740, TPS25740A

SLVSDG8B - APRIL 2016 - REVISED JUNE 2017

# TPS25740, TPS25740A USB Type-C and USB PD Source Controller

### 1 Features

- USB Power Delivery (PD) 2.0 Certified Provider, USB Type-C<sup>™</sup> Rev. 1.2 Compliant Source

- Pin-Selectable Voltage Advertisement

- 5 V, 12 V, and/or 20 V (TPS25740)

- 5 V, 9 V, and/or 15 V (TPS25740A)

- Pin-Selectable Peak Power Settings

- 12 options 15 W 100W (TPS25740)

- 11 options 15 W 81W (TPS25740A)

- High Voltage and Safety Integration

- Overvoltage, Overcurrent, Overtemperature Protection and V<sub>BUS</sub> Discharge

- IEC 61000-4-2 Protection on CC1 and CC2

- Input Pin for Fast Shutdown Under Fault

- Control of External N-ch MOSFET

- 2-pin External Power Supply Control

- Wide VIN Supply (4.65 V 25 V)

- Below 10 µA Quiescent Current when Unattached

- Port Attachment Indicator

- · Port Power Management

- · Built-In 1.8 V at 35 mA Supply Output

# 2 Applications

- USB-PD Adaptor (data-less)

- Dedicated Charging Port (data-less)

- Power Hub (data-less)

- Power Bank

- Cigarette Lighter Adaptor (CLA)

# 3 Description

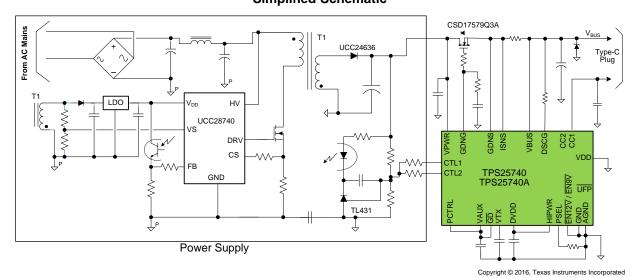

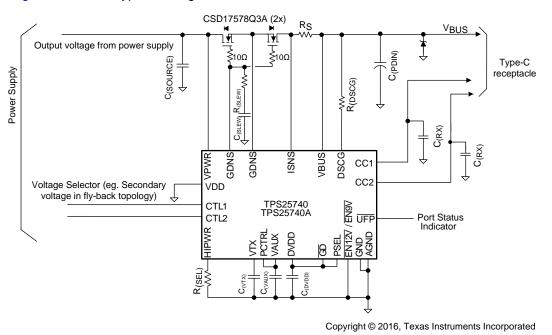

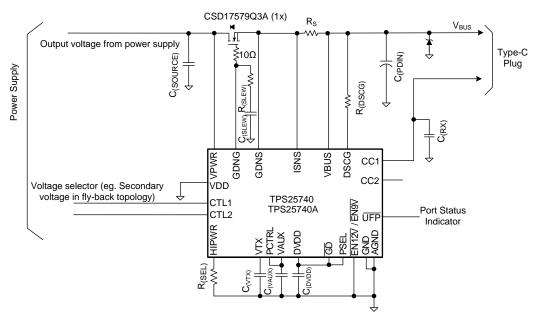

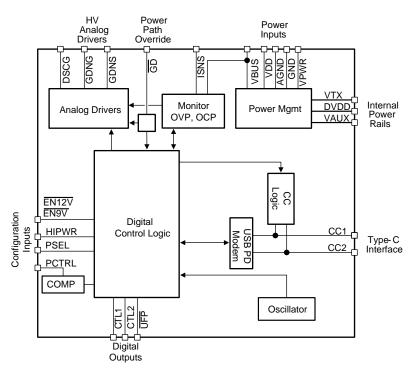

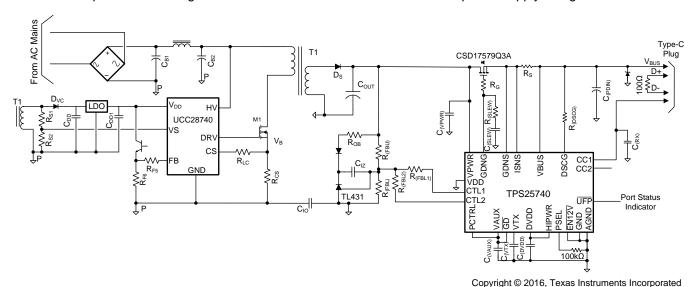

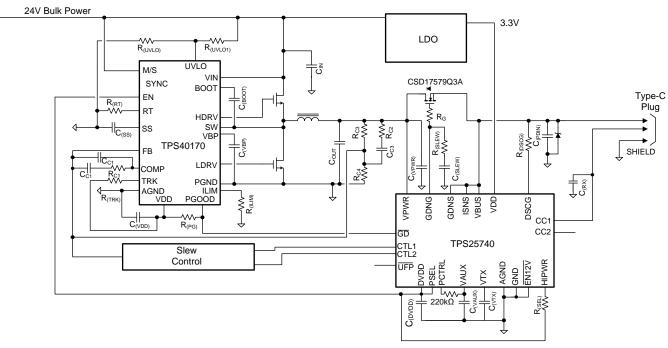

The TPS25740, TPS25740A implements a source that is compliant to USB Power Delivery 2.0 version 1.2 and Type-C revision 1.2. It monitors the CC pin to detect when a USB Type-C sink is attached, then it enables a N-ch MOSFET gate driver to turn on VBUS. The device then offers up to three different voltages using USB Power Delivery. Four input pins (PSEL, HIPWR, PCTRL, and (EN12V or EN9V) are used to configure the voltages and currents advertised. The device uses the CTL1 and CTL2 pins to select one of three voltages from the power supply based on the voltage requested by the attached sink. The device automatically handles discharging the VBUS output per USB PD requirements.

The TPS25740, TPS25740A typically draws  $8.5 \mu A$  (or  $5.8 \mu A$  if VDD = 3.3 V) when no device is attached. Additional system power saving is achievable by using the Port Attachment Indicator (UFP) output to disable the power source when no device is attached.

Protection features include overvoltage protection, overcurrent protection, over-temperature protection, IEC for CC pins, and system override to disable the gate driver (GD).

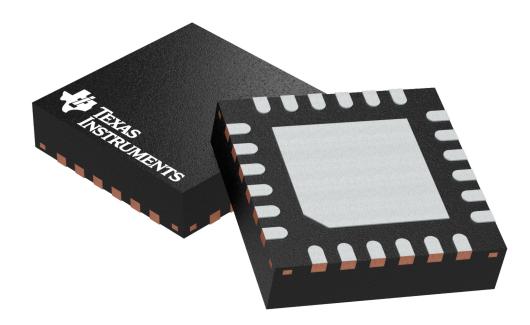

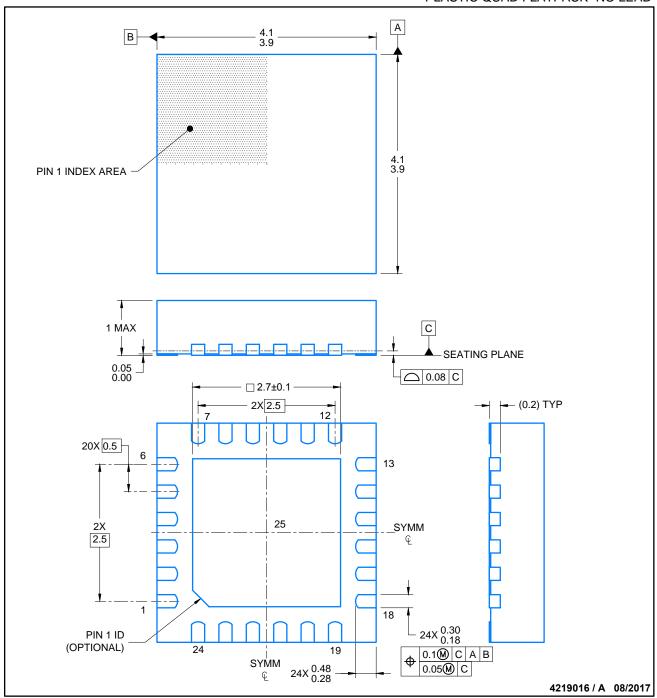

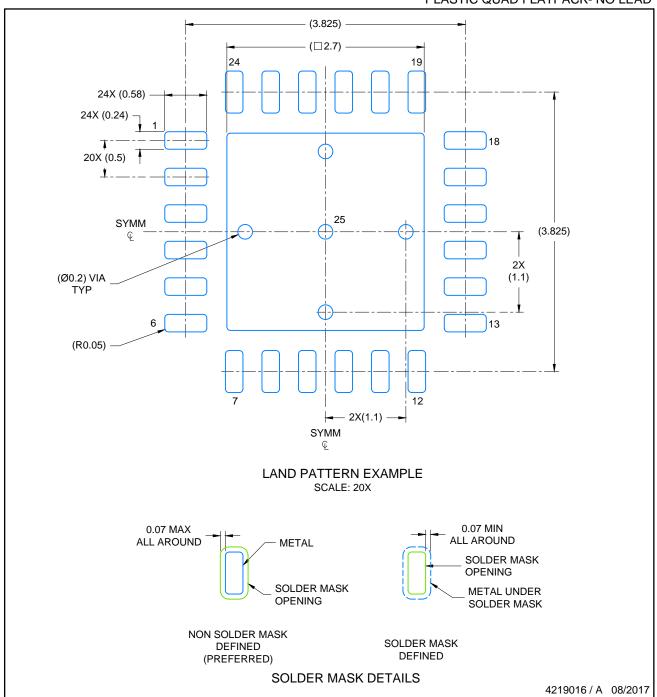

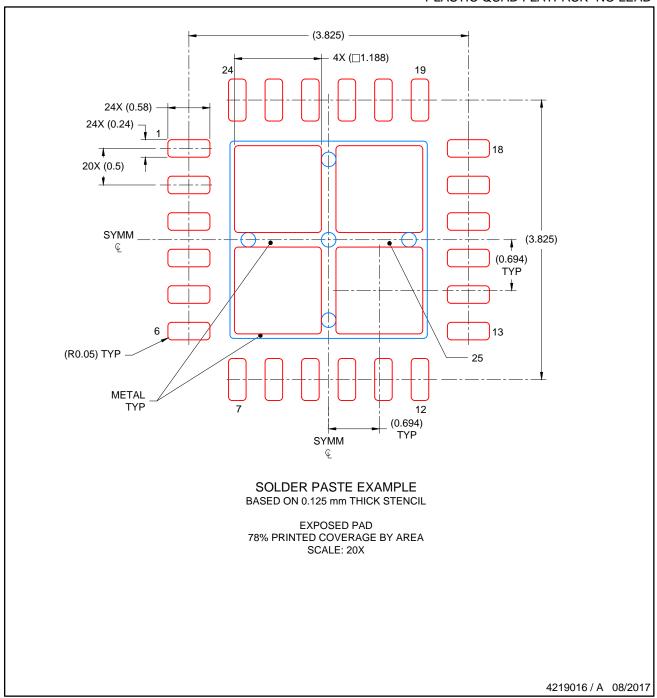

### Device Information<sup>(1)</sup>

| PAR   | T NUMBER | PACKAGE  | BODY SIZE (NOM)   |

|-------|----------|----------|-------------------|

| TPS25 | 740      | OEN (24) | 4.00 mm v 4.00 mm |

| TPS25 | 740A     | QFN (24) | 4.00 mm x 4.00 mm |

For all available packages, see the orderable addendum at the end of the data sheet.

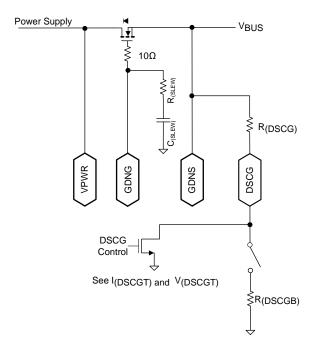

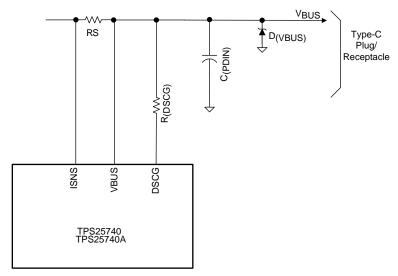

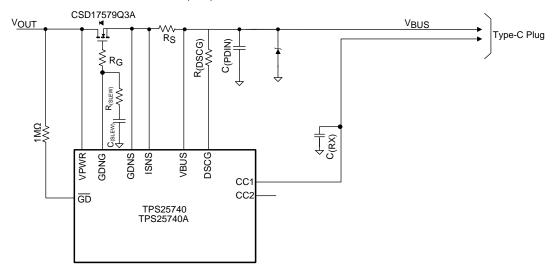

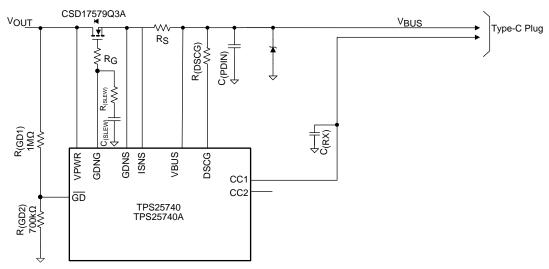

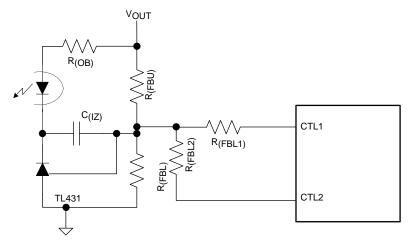

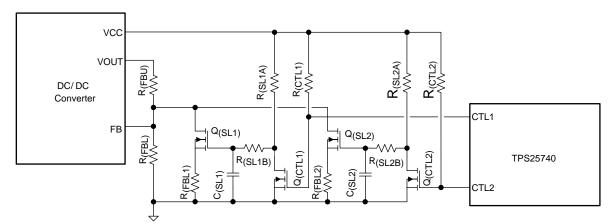

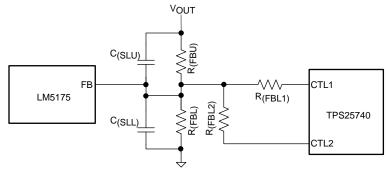

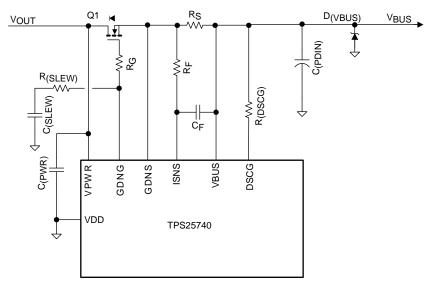

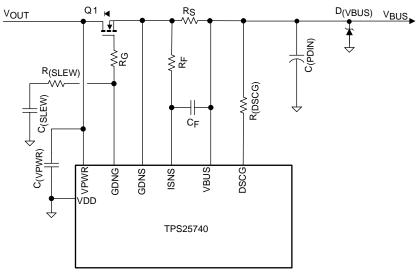

# **Simplified Schematic**

# **Table of Contents**

| 1 | Features 1                                                                                                                                                                                                        |    | 9.1 Application Information                                                                                                                                                           |

|---|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2 | Applications 1                                                                                                                                                                                                    |    | 9.2 Typical Application , A/C Power Source (Wall                                                                                                                                      |

| 3 | Description 1                                                                                                                                                                                                     |    | Adapter)                                                                                                                                                                              |

| 4 | Revision History2                                                                                                                                                                                                 |    | 9.3 System Examples                                                                                                                                                                   |

| 5 | Device Comparison Table 4                                                                                                                                                                                         | 10 | Power Supply Recommendations 54                                                                                                                                                       |

| 6 | Pin Configuration and Functions 4                                                                                                                                                                                 |    | 10.1 VDD                                                                                                                                                                              |

| 7 | Specifications6                                                                                                                                                                                                   | 11 | Layout 55                                                                                                                                                                             |

|   | 7.1 Absolute Maximum Ratings       6         7.2 ESD Ratings       6                                                                                                                                              |    | 11.1 Port Current Kelvin Sensing                                                                                                                                                      |

|   | 7.3 Recommended Operating Conditions                                                                                                                                                                              | 12 | 11.3 Layout Example                                                                                                                                                                   |

| 8 | 7.5 Electrical Characteristics       8         7.6 Timing Requirements       11         7.7 Switching Characteristics       12         7.8 Typical Characteristics       16         Detailed Description       18 | 12 | 12.1     Documentation Support     5       12.2     Related Links     5       12.3     Receiving Notification of Documentation Updates     5       12.4     Community Resources     5 |

|   | 8.1 Overview       18         8.2 Functional Block Diagram       20         8.3 Feature Description       20         8.4 Device Functional Modes       35                                                         | 13 | 12.5 Trademarks                                                                                                                                                                       |

| 9 | Application and Implementation 36                                                                                                                                                                                 |    | mornauon                                                                                                                                                                              |

# 4 Revision History

| CI | hanges from Revision A (May 2016) to Revision B                                                                                                                                          | Page       |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| •  | Added Feature: Port Power Management                                                                                                                                                     | 1          |

| •  | Changed the Input resistance MAX value From: 5 M $\Omega$ To: 6 M $\Omega$ in the <i>Electrical Characteristics</i> table                                                                | 9          |

| •  | Changed the unloaded output voltage on CC pin, V <sub>(OCN)</sub> MIN value From: 2.8 V To: 2.7 V and the MAX value From 5.5 V To: 4.35 V in the <i>Electrical Characteristics</i> table |            |

| •  | Deleted t <sub>WD</sub> Watchdog Timer From the <i>Timing Requirements</i> table                                                                                                         | <b>1</b> 1 |

| •  | Changed the t <sub>ST</sub> TYP value From: 24 ms To: 30 ms in the Switching Characteristics table                                                                                       | 12         |

| •  | Deleted sentence from <i>Output Power Supply (DVDD)</i> : "It will also be pulsed high for t <sub>CcDeb</sub> every t <sub>WD</sub> when there is nothing connected."                    | 34         |

| •  | Deleted the last sentence from the <i>Sleep Mode</i> section: "The device also wakes up every t <sub>WD</sub> and checks for a connection before returning to sleep mode."               | 35         |

| •  | Added test: "The TPS25740/TPS25740A Design Calculator Tool" to the Application Information section                                                                                       | 36         |

| •  | Changed capacitor From: 10 µF To: 6.8 µF in the Figure 36                                                                                                                                | 36         |

| •  | Added sentence "All slew rate control methods" to the Voltage Transition Requirements section                                                                                            | <b>4</b> 1 |

| •  | Changed section title From: V <sub>OUT</sub> Ripple Filtering using R <sub>F</sub> and C <sub>F</sub> To: Tuning OCP Using R <sub>F</sub> and C <sub>F</sub> . Updated section text      | 43         |

| •  | Changed From: A 10 μF, 25 V, ±10% X5R or X7R ceramic capacitor To: A 6.8 μF, 25 V, ±10% X5R or X7R ceramic capacitor in the <i>Configurable Components</i> section                       |            |

| •  | Changed From: "Type-C receptacle" To: "Type-C plug" in Figure 56                                                                                                                         | 48         |

| •  | Changed From: A 10 μF, 25 V, ±10% X5R or X7R ceramic capacitor to: A 6.8 μF, 25 V, ±10% X5R or X7R ceramic capacitor in the <i>Configurable Components</i> section                       |            |

| •  | Changed section title From: Dual-Port A/C Power Source (Wall Adaptor) To: Dual-Port Power Managed A/C Power Source (Wall Adaptor)                                                        | 53         |

| •  | Added the TPS25740/TPS25740A Design Calculator Tool link and the TPS25740EVM-741 and TPS25740AEVM-741 EVM User's Guide link to the <i>Documentation Support</i> section                  | 57         |

| Cł | nanges from Original (March 2016) to Revision A   | Pag | • |

|----|---------------------------------------------------|-----|---|

| •  | Changed From: Product Preview To: Production Data |     | • |

# 5 Device Comparison Table

| DEVICE NUMBER | VOLTAGE OPTION             |

|---------------|----------------------------|

| TPS25740      | Offers 5 V, 12 V, and 20 V |

| TPS25740A     | Offers 5 V, 9 V, and 15 V  |

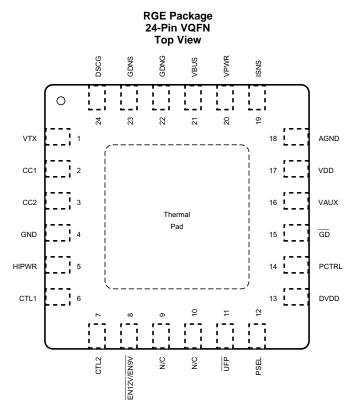

# 6 Pin Configuration and Functions

**Pin Functions**

| PIN NAME NO. |    | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                  |  |  |

|--------------|----|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|              |    | 1/0 |                                                                                                                                                                                                                                                                              |  |  |

| VTX          | 1  | 0   | Bypass pin for transmit driver supply. Connect this pin to GND via the recommended ceramic capacitor.                                                                                                                                                                        |  |  |

| CC1          | 2  | I/O | Multifunction configuration channel interface pin to USB Type-C. Functions include connector polarity, end-device connection detect, current capabilities, and PD communication.                                                                                             |  |  |

| CC2          | 3  | I/O | tifunction configuration channel interface pin to USB Type-C. Functions include connector polarity, l-device connection detect, current capabilities, and PD communication.                                                                                                  |  |  |

| GND          | 4  | _   | Power ground is associated with power management and gate driver circuits. Connect to AGND and PAD.                                                                                                                                                                          |  |  |

| HIPWR        | 5  | I   | Four-state input pin used to configure the voltages and currents that will be advertised. It may be connected directly to GND or DVDD, or it may be connected to GND or DVDD via a resistance R <sub>(SEL)</sub> .                                                           |  |  |

| CTL1         | 6  | 0   | Digital output pin used to control an external voltage regulator.                                                                                                                                                                                                            |  |  |

| CTL2         | 7  | 0   | Digital output pin used to control an external voltage regulator.                                                                                                                                                                                                            |  |  |

| EN12V / EN9V | 8  | ı   | For TPS25740: If it is pulled low, then the 12 V PDO may be transmitted. If it is not pulled low, the 12-V PDO will not be advertised. For TPS25740A: If it is pulled low, then the 9 V PDO may be transmitted. If it is not pulled low, the 9-V PDO will not be advertised. |  |  |

| N/C          | 9  |     | Connect to GND.                                                                                                                                                                                                                                                              |  |  |

| N/C          | 10 |     | Connect to GND.                                                                                                                                                                                                                                                              |  |  |

Submit Documentation Feedback

# Pin Functions (continued)

|       | PIN | 1/0 | PERCENTION                                                                                                                                                                                           |  |  |

|-------|-----|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME  | NO. | 1/0 | DESCRIPTION                                                                                                                                                                                          |  |  |

| UFP   | 11  | 0   | Open drain output pin used to indicate that either CC1 or CC2 (but not both) is pulled down by a USB Type-C Sink.                                                                                    |  |  |

| PSEL  | 12  | 1   | A four-state input used for selecting the maximum power that can be provided. It may be connected directly to GND or DVDD, or it may be connected to GND or DVDD via a resistance R <sub>(SEL)</sub> |  |  |

| DVDD  | 13  | 0   | Internally regulated 1.85 V rail for external use up to 35 mA. Connect this pin to GND via the recommended bypass capacitor .                                                                        |  |  |

| PCTRL | 14  | I   | Input pin used to control the power that will be advertised. It may be pulled high or low dynamically.                                                                                               |  |  |

| GD    | 15  | 1   | Master enable for the GDNG/GDNS gate driver. The system can drive this low to force the power path switch off.                                                                                       |  |  |

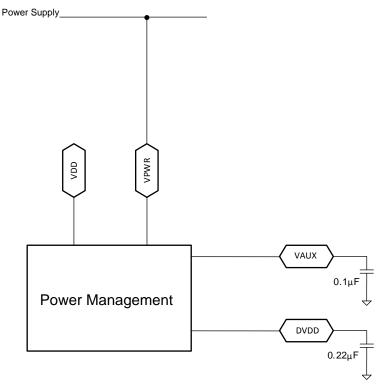

| VAUX  | 16  | 0   | Internally regulated rail for use by the power management circuits. Connect this pin to GND via the recommended bypass capacitor.                                                                    |  |  |

| VDD   | 17  | 1   | Optional input supply.                                                                                                                                                                               |  |  |

| AGND  | 18  | _   | Analog ground associated with monitoring and power conditioning circuits. Connect to GND and PAD.                                                                                                    |  |  |

| ISNS  | 19  | 1   | The ISNS input is used to monitor a VBUS-referenced sense resistor for over-current events.                                                                                                          |  |  |

| VPWR  | 20  | I   | Connect to an external voltage as a source of bias power. If VDD is supplied, this supply is optional while UFP is high.                                                                             |  |  |

| VBUS  | 21  | I   | The voltage monitor for the VBUS line.                                                                                                                                                               |  |  |

| GDNG  | 22  | 0   | High-voltage open drain gate driver which may be used to drive NMOS power switches. Connect to the gate terminal.                                                                                    |  |  |

| GDNS  | 23  | I   | High-voltage open drain gate driver which may be used to drive NMOS power switches. Connect to the source terminal.                                                                                  |  |  |

| DSCG  | 24  | 0   | Discharge is an open-drain output that discharges the system VBUS line through an external resistor.                                                                                                 |  |  |

| PAD   |     |     | Connect PAD to GND / AGND plane.                                                                                                                                                                     |  |  |

# 7 Specifications

### 7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                                                                                                                               |                                                     | MIN       | MAX                | UNIT |

|-------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|-----------|--------------------|------|

|                                                                                                                               | VDD , EN12V, EN9V, CTL1, CTL2, UFP, PCTRL, CC1, CC2 | -0.3      | 6                  | V    |

| Pin Voltage (sustained)                                                                                                       | VTX <sup>(2)</sup>                                  | -0.3      | 2.1                | V    |

|                                                                                                                               | VAUX <sup>(2)</sup>                                 | -0.3      | 4.5                | V    |

|                                                                                                                               | <u>GD</u> <sup>(3)</sup>                            | -0.3      | 7                  | V    |

|                                                                                                                               | HIPWR, PSEL, DVDD (2)                               | -0.3      | 2.1                | V    |

|                                                                                                                               | GDNG <sup>(2)</sup>                                 | -0.5      | 40                 | V    |

|                                                                                                                               | VBUS,VPWR, ISNS, DSCG, GDNS                         | -0.5      | 30                 | V    |

| Pin Voltage (transient for 1ms)                                                                                               | VBUS,VPWR, ISNS, DSCG, GDNS                         | -1.5      | 30                 | V    |

|                                                                                                                               | $V_{(GDNG)} - V_{(GDNS)}$                           | -0.3      | 20                 | V    |

| Pin-to-pin voltage                                                                                                            | AGND to GND                                         | -0.3      | 0.3                | V    |

|                                                                                                                               | ISNS to VBUS                                        | -0.3      | 0.3                | V    |

|                                                                                                                               | CTL1, CTL2, UFP                                     |           | 8                  | mA   |

| Sinking current (average)                                                                                                     | GD                                                  |           | 100                | μA   |

|                                                                                                                               | DSCG                                                |           | 10                 | mA   |

| Sinking current (transient, 50 ms pulse 0.25% duty cycle)                                                                     | DSCG                                                |           | 375                | mA   |

|                                                                                                                               | VTX                                                 | Internall | Internally limited |      |

| Pin Voltage (transient for 1ms)  Pin-to-pin voltage  Sinking current (average)  Sinking current (transient, 50 ms pulse 0.25% | CC1, CC2                                            | Internall | y limited          | mA   |

|                                                                                                                               | VAUX                                                | 0         | 25                 | μA   |

| Operating junction temperature range, T <sub>J</sub>                                                                          |                                                     | -40       | 125                | °C   |

| Storage temperature, T <sub>stg</sub>                                                                                         |                                                     | -65       | 150                | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) Do not apply voltage to these pins.

# 7.2 ESD Ratings<sup>(1)</sup>

|                    |                                        |                                                                                | VALUE  | UNIT |

|--------------------|----------------------------------------|--------------------------------------------------------------------------------|--------|------|

|                    |                                        | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 (2)                         | ±2500  |      |

| V <sub>(ESD)</sub> | Charged-device model (CDM), p C101 (3) | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(3)</sup> | ±1000  | V    |

| (202)              | v                                      | IEC <sup>(4)</sup> 61000-4-2 contact discharge, CC1, CC2                       | ±8000  |      |

|                    |                                        | IEC <sup>(4)</sup> 61000-4-2 air-gap discharge, CC1, CC2                       | ±15000 |      |

<sup>(1)</sup> This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

Submit Documentation Feedback

Voltage allowed to rise above Absolute Maximum provided current is limited.

<sup>(2)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

<sup>(3)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

<sup>(4)</sup> These results were passing limits that were obtained on an application-level test board. Individual results may vary based on implementation. Surges per IEC61000-4-2, 1999 applied between CC1/CC2 and ground of TPS25740EVM-741 and TPS25740AEVM-741

# 7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                     | -                              |                                                               | MIN   | NOM  | MAX   | UNIT |

|---------------------|--------------------------------|---------------------------------------------------------------|-------|------|-------|------|

| \ /                 | Complex Voltage                | VDD                                                           | 0     |      | 5.5   | V    |

| $V_{IN}$            | Supply Voltage                 | VPWR                                                          | 4.65  |      | 25    | V    |

|                     |                                | EN12V, EN9V, PCTRL, CC1, CC2, CTL1, CTL2                      | 0     |      | 5.5   | V    |

| $V_{I}$             | Applied Voltage                | GD                                                            | 0     |      | 6.5   | V    |

|                     |                                | DSCG, GDNS, VBUS                                              | 0     |      | 25    | V    |

|                     |                                | HIPWR, PSEL                                                   | 0     |      | DVDD  | V    |

| $V_{I}$             | Pin-to-pin voltage             | ISNS - VBUS                                                   | -0.1  |      | 0.1   | V    |

|                     |                                | EN12V, EN9V                                                   | 1.4   |      |       | V    |

| $V_{IH}$            | High-Level Input Voltage       | PCTRL                                                         | 2     |      |       | V    |

|                     |                                | GD                                                            | 2     |      |       | V    |

|                     |                                | EN12V, EN9V                                                   |       |      | 0.5   | V    |

| V <sub>IL</sub>     | Low-Level Input Voltage        | PCTRL                                                         |       |      | 1.6   | V    |

|                     |                                | GD                                                            |       |      | 1.6   | V    |

|                     | Sinking Current                | CTL1, CTL2, UFP                                               |       |      | 5     | mA   |

|                     |                                | GD                                                            |       |      | 80    | μΑ   |

| I <sub>S</sub>      |                                | DSCG, transient sinking current 50 ms pulse, 0.25% duty cycle |       |      | 350   | mA   |

|                     |                                | DSCG, average                                                 |       |      | 5     | mA   |

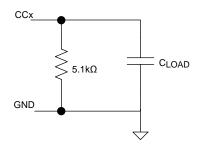

|                     |                                | CC1, CC2 (C <sub>(RX)</sub> )                                 | 200   | 560  | 600   | pF   |

|                     |                                | VBUS (C <sub>(PDIN)</sub> )                                   |       |      | 10    | μF   |

| 0                   | Shunt capacitance              | DVDD (C <sub>(DVDD)</sub> )                                   | 0.198 | 0.22 | 0.242 | μF   |

| C <sub>S</sub>      |                                | VAUX (C <sub>(VAUX)</sub> )                                   | 0.09  | 0.1  | 0.11  | μF   |

|                     |                                | VTX (C <sub>(VTX)</sub> )                                     | 0.09  | 0.10 | 0.11  | μF   |

|                     |                                | VDD (C <sub>(VDD)</sub> )                                     | 0.09  |      |       | μF   |

| D                   | Company resistance             | Configured for 3 A                                            |       | 5    | 6.4   | mΩ   |

| R <sub>S</sub>      | Sense resistance               | Configured for 5 A                                            |       | 5    | 5.8   | mΩ   |

| R <sub>(PUD)</sub>  | Pull up/down resistance        | HIPWR, PSEL (direct to GND or direct to DVDD)                 | 0     |      | 1     | kΩ   |

| (1 00)              | ·                              | HIPWR, PSEL (R <sub>(SEL)</sub> )                             | 80    | 100  | 120   | kΩ   |

|                     |                                | Maximum VBUS voltage of 25 V                                  | 80    |      |       | Ω    |

| R <sub>(DSCG)</sub> | Series resistance              | Maximum VBUS voltage of 15 V                                  | 43    |      |       | Ω    |

| /                   |                                | Maximum VBUS voltage of 6 V                                   | 20    |      |       | Ω    |

| TJ                  | Operating junction temperature |                                                               | -40   |      | 125   | °C   |

## 7.4 Thermal Information

|                        | 40                                           | TPS25740<br>TPS25740A |      |

|------------------------|----------------------------------------------|-----------------------|------|

|                        | THERMAL METRIC <sup>(1)</sup>                | RGE (VQFN)            | UNIT |

|                        |                                              | 24 PINS               |      |

| $R_{\theta JA}$        | Junction-to-ambient thermal resistance       | 33                    | °C/W |

| $R_{\theta JC(top)}$   | Junction-to-case (top) thermal resistance    | 32.6                  | °C/W |

| $R_{\theta JB}$        | Junction-to-board thermal resistance         | 10                    | °C/W |

| ΨЈТ                    | Junction-to-top characterization parameter   | 0.4                   | °C/W |

| ΨЈВ                    | Junction-to-board characterization parameter | 10                    | °C/W |

| R <sub>θ</sub> JC(bot) | Junction-to-case (bottom) thermal resistance | 2.6                   | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

## 7.5 Electrical Characteristics

Unless otherwise stated in a specific test condition the following conditions apply:  $-40^{\circ}\text{C} \le \text{T}_{\text{J}} \le 125^{\circ}\text{C}$ ;  $3 \le \text{VDD} \le 5.5 \text{ V}$ ,  $4.65 \text{ V} \le \text{VPWR} \le 25 \text{ V}$ ; HIPWR = GND, PSEL = GND,  $\overline{\text{GD}} = \text{VAUX}$ , PCTRL = VAUX, AGND = GND; VAUX, VTX, bypassed with 0.1  $\mu$ F, DVDD bypassed with 0.22  $\mu$ F,  $\overline{\text{EN12V}} = \text{GND}$  and  $\overline{\text{EN9V}} = \text{GND}$ ; all other pins open (unless otherwise noted)

|                         | PARAMETER                              | TEST CONDITIONS                                                                                                    | MIN   | TYP         | MAX  | UNIT |

|-------------------------|----------------------------------------|--------------------------------------------------------------------------------------------------------------------|-------|-------------|------|------|

| Voltage Con             | nparator (VBUS)                        |                                                                                                                    |       |             |      |      |

| V <sub>(VBUS RTH)</sub> | VBUS Threshold (Rising voltage)        |                                                                                                                    | 4.25  | 4.45        | 4.65 | V    |

| V <sub>(VBUS_FTH)</sub> | VBUS Threshold (Falling voltage)       |                                                                                                                    | 3.5   | 3.7         | 3.9  | V    |

| ( /                     | VBUS Threshold (Hysteresis)            |                                                                                                                    |       | 0.75        |      | V    |

| Power Supp              | ly (VDD, VPWR)                         |                                                                                                                    |       |             |      |      |

|                         |                                        | Rising voltage                                                                                                     | 2.8   | 2.91        | 2.97 |      |

|                         |                                        | Falling voltage                                                                                                    | 2.8   | 2.86        | 2.91 | V    |

| $V_{(VDD\_TH)}$         | VDD UVLO threshold                     | Hysteresis, comes into effect once the rising threshold is crossed.                                                |       | 0.05        |      | V    |

| V <sub>(VPWR_RTH)</sub> | VPWR UVLO threshold rising             | Rising voltage                                                                                                     | 4.2   | 4.45        | 4.65 | V    |

| V <sub>(VPWR_FTH)</sub> | VPWR UVLO threshold falling            | Falling voltage                                                                                                    | 3.5   | 3.7         | 3.9  | V    |

| (,                      | VPWR UVLO threshold hysteresis         | Hysteresis, comes into effect once the rising threshold is crossed.                                                |       | 0.75        |      | V    |

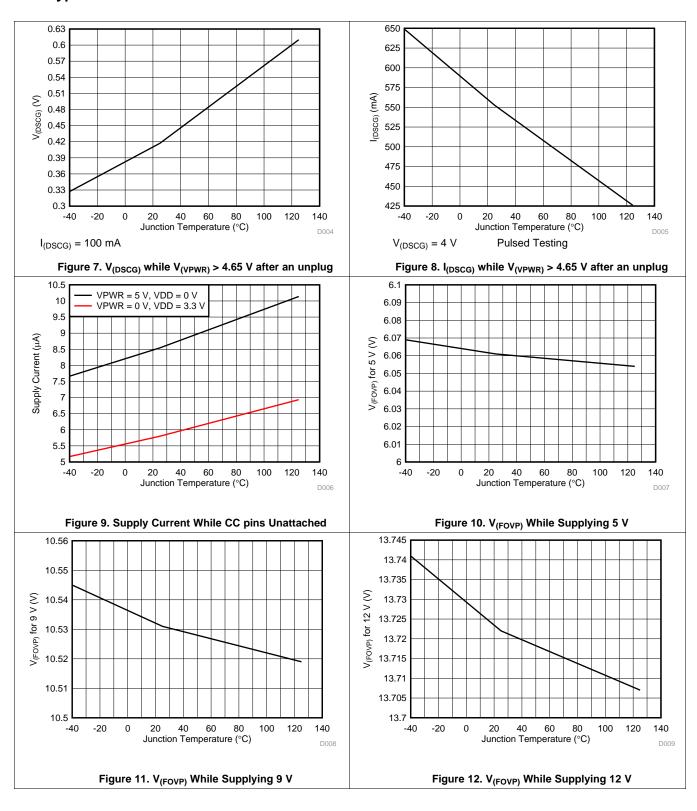

|                         | Supply current drawn from VDD in sleep | VPWR = 0 V, VDD = 5 V, CC1 and CC2 pins are open.                                                                  |       | 9.2         | 20   | μA   |

|                         | mode                                   | VPWR = 0 V, VDD = 5 V,CC1 pin open,<br>CC2 pin tied to GND.                                                        |       | 94          | 150  | μΑ   |

|                         | Supply current drawn from VPWR in      | VPWR = 5 V, VDD = 0 V, CC1 and CC2 pins are open.                                                                  |       | 8.5         | 15   | μΑ   |

|                         | sleep mode                             | VPWR = 5 V, VDD = 0 V, CC1 pin open, CC2 pin tied to GND.                                                          |       | 90          | 140  | μΑ   |

| I <sub>(SUPP)</sub>     | Operating current while sink attached  | PD Sourcing active, VBUS = 5 V,<br>VPWR = 5 V, VDD = 3.3 V                                                         | 1     | 1.8         | 3    | mA   |

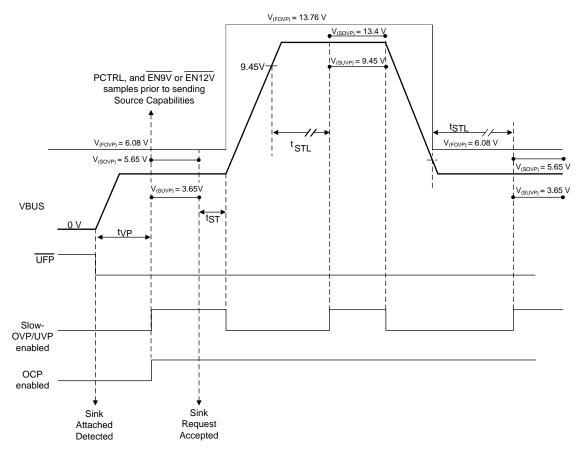

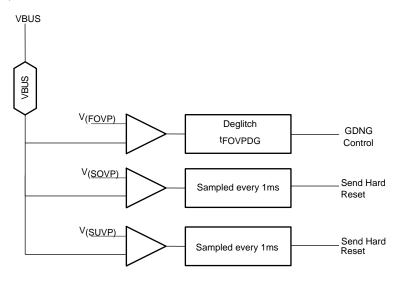

| Over/Under              | Voltage Protection (VBUS)              |                                                                                                                    |       |             |      |      |

|                         |                                        | 5 V PD contract                                                                                                    | 5.8   | 6.05        | 6.3  | V    |

|                         | Fast OVP threshold, always enabled     | 12 V PD contract (TPS25740)                                                                                        | 13.2  | 13.75       | 14.3 | V    |

| $V_{(FOVP)}$            |                                        | 20 V PD contract (TPS25740)                                                                                        | 22.1  | 23.05       | 24.0 | V    |

|                         |                                        | 9 V PD contract (TPS25740A)                                                                                        | 10.1  | 10.55       | 11.0 | V    |

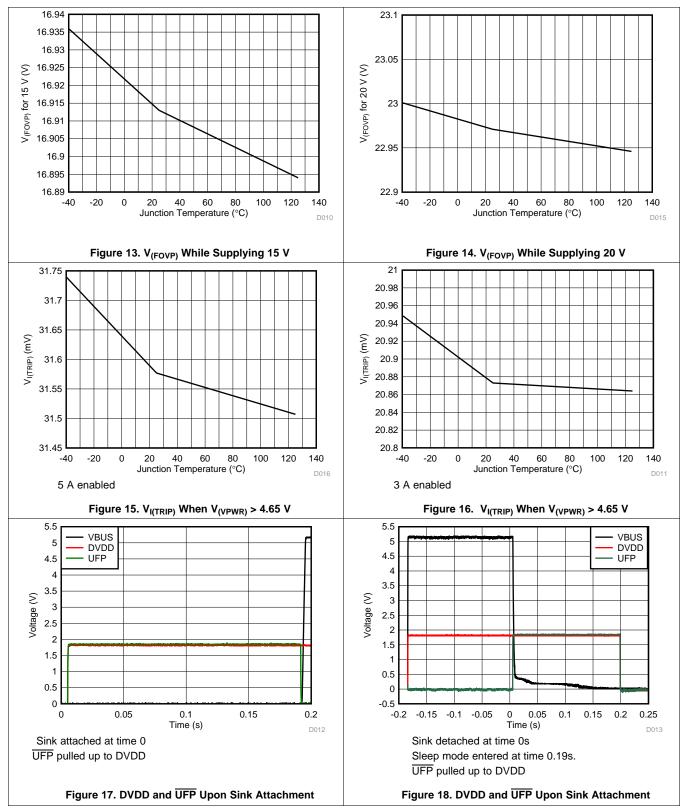

|                         |                                        | 15 V PD contract (TPS25740A)                                                                                       | 16.2  | 16.95       | 17.7 | V    |

|                         |                                        | 5 V PD contract                                                                                                    | 5.5   | 5.65        | 5.8  | V    |

|                         |                                        | 12 V PD contract (TPS25740)                                                                                        | 13.1  | 13.4        | 13.7 | V    |

| V <sub>(SOVP)</sub>     | Slow OVP threshold, disabled during    | 20 V PD contract (TPS25740)                                                                                        | 21.5  | 22.0        | 22.5 | V    |

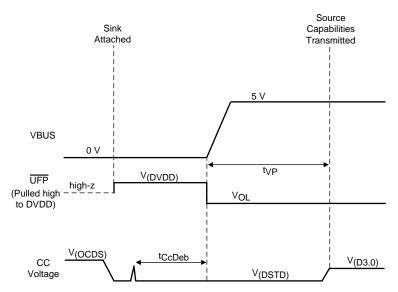

| (0011)                  | voltage transitions. (See Figure 1)    | 9 V PD contract (TPS25740A)                                                                                        | 10    | 10.2        | 10.4 | V    |

|                         |                                        | 15 V PD contract (TPS25740A)                                                                                       | 16.3  | 16.5        | 17   | V    |

|                         |                                        | 5 V PD contract                                                                                                    | 3.5   | 3.65        | 3.8  | V    |

|                         |                                        | 12 V PD contract (TPS25740)                                                                                        | 9.2   | 9.45        | 9.7  | V    |

| V <sub>(SUVP)</sub>     | UVP threshold, disabled during voltage | 20 V PD contract (TPS25740)                                                                                        | 15.7  | 16.1        | 16.5 | V    |

| (SUVF)                  | transitions (See Figure 1)             | 9 V PD contract (TPS25740A)                                                                                        | 6.8   | 6.95        | 7.1  | V    |

|                         |                                        | 15 V PD contract (TPS25740A)                                                                                       | 11.7  | 11.95       | 12.2 | V    |

| VAUX                    | 1                                      |                                                                                                                    | 11.1  | 11.55       | 12.2 | v    |

| V <sub>(VAUX)</sub>     | Output voltage                         | $0 \le I_{(VALJX)} \le I_{(VALJXEXT)}$                                                                             | 2.875 | 3.2         | 4.1  | V    |

| - (VAUX)                | VAUX Current limit                     | (VAUA) - (VAUAEAT)                                                                                                 | 1     | J. <u>L</u> | 5    | mA   |

|                         | External load that may be applied to   |                                                                                                                    | '     |             |      |      |

| (VAUXEXT)               | VAUX.                                  |                                                                                                                    |       |             | 25   | μA   |

| DVDD                    |                                        |                                                                                                                    |       |             | 1    |      |

| $V_{(DVDD)}$            | Output voltage                         | 0 mA ≤ $I_{(DVDD)}$ ≤ 35 mA, CC1 or CC2 pulled to ground via 5.1 kΩ, or both CC1 and CC2 pulled to ground via 1 kΩ | 1.75  | 1.85        | 1.95 | V    |

|                         | Load Regulation                        | Overshoot from V <sub>(DVDD)</sub> , 10-mA minimum, 0.198-µF bypass capacitor                                      | 1.7   |             | 2    | V    |

|                         | Current limit                          | DVDD tied to GND                                                                                                   | 40    |             | 150  | mA   |

Submit Documentation Feedback

# **Electrical Characteristics (continued)**

Unless otherwise stated in a specific test condition the following conditions apply:  $-40^{\circ}\text{C} \leq T_{\text{J}} \leq 125^{\circ}\text{C}$ ;  $3 \leq \text{VDD} \leq 5.5 \text{ V}$ ,  $4.65 \text{ V} \leq \text{VPWR} \leq 25 \text{ V}$ ; HIPWR = GND, PSEL = GND,  $\overline{\text{GD}} = \text{VAUX}$ , PCTRL = VAUX, AGND = GND; VAUX, VTX, bypassed with  $0.1 \, \mu\text{F}$ , DVDD bypassed with  $0.22 \, \mu\text{F}$ ,  $\overline{\text{EN12V}} = \text{GND}$  and  $\overline{\text{EN9V}} = \text{GND}$ ; all other pins open (unless otherwise noted)

|                         | PARAMETER                            | TEST CONDITIONS                                                                                                                | MIN   | TYP   | MAX   | UNIT      |

|-------------------------|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|-----------|

| VTX                     |                                      |                                                                                                                                |       |       |       |           |

|                         | Output voltage                       | Not transmitting or receiving, 0 to 2 mA external load                                                                         | 1.050 | 1.125 | 1.200 | V         |

|                         | Current Limit                        | VTX tied to GND                                                                                                                | 2.5   |       | 10    | mA        |

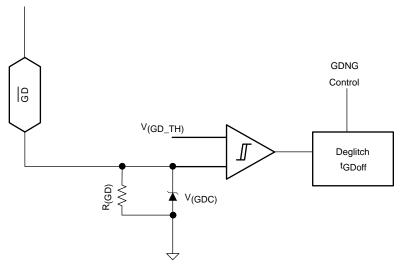

| Gate Driver             | Disable (GD)                         |                                                                                                                                |       |       |       |           |

| ·                       | Innuit anable threehold valters      | Rising voltage                                                                                                                 | 1.64  | 1.725 | 1.81  | V         |

| $V_{(GD\_TH)}$          | Input enable threshold voltage       | Hysteresis                                                                                                                     |       | 0.15  |       | V         |

| V <sub>(GDC)</sub>      | Internal clamp voltage               | I <sub>(GD)</sub> = 80 μA                                                                                                      | 6.5   | 7     | 8.5   | V         |

| R <sub>(GD)</sub>       | Internal pulldown resistance         | From 0 V to 6 V                                                                                                                | 3     | 6     | 9.5   | ΜΩ        |

| Discharge (             | DSCG) (1)(2)                         |                                                                                                                                |       |       |       |           |

| V <sub>(DSCGT)</sub>    | ON state (linear)                    | I <sub>(DSCG)</sub> = 100 mA                                                                                                   | 0.15  | 0.42  | 1     | V         |

| I <sub>(DSCGT)</sub>    | ON state (saturation)                | V <sub>(DSCG)</sub> = 4 V, pulsed mode operation                                                                               | 220   | 553   | 1300  | mA        |

| R <sub>(DSCGB)</sub>    | Discharge bleeder                    | While CC1 is pulled down by 5.1 k $\Omega$ and CC2 is open, V <sub>(DSCG)</sub> = 25 V                                         | 6.6   | 8.2   | 10    | kΩ        |

|                         | Leakage current                      | 0 V ≤ V <sub>(DSCG)</sub> ≤ 25 V                                                                                               |       |       | 2     | μA        |

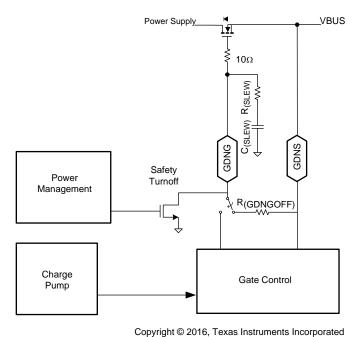

| N-ch MOSF               | ET Gate Driver (GDNG,GDNS)           | •                                                                                                                              |       |       |       |           |

| I <sub>(GDNON)</sub>    | Sourcing current                     | $0 \text{ V} \le V_{\text{(GDNS)}} \le 25 \text{ V}, \\ 0 \text{ V} \le V_{\text{(GDNG)}} - V_{\text{(GDNS)}} \le 6 \text{ V}$ | 13.2  | 20    | 30    | μΑ        |

| .,                      | Sourcing voltage while enabled       | 0 V $\leq$ V <sub>(GDNS)</sub> $\leq$ 25 V, I <sub>(GDNON)</sub> $\leq$ 4 $\mu$ A, VPWR = 0 V                                  | 7     |       | 12    | V         |

| V <sub>(GDNON)</sub>    | $(V_{(GDNG)} - V_{(GDNS)})$          | 0 V $\leq$ V <sub>(GDNS)</sub> $\leq$ 25 V, I <sub>(GDNON)</sub> $\leq$ 4 $\mu$ A, VDD = 0 V                                   | 8.5   |       | 12    | V         |

| R <sub>(GDNGOFF)</sub>  | Sinking strength while disabled      | $V_{(GDNG)} - V_{(GDNS)} = 0.5 \text{ V},$ $0 \le V_{(GDNS)} \le 25 \text{ V}$                                                 |       | 150   | 300   | Ω         |

|                         | Sinking strength UVLO (safety)       | $VDD = 1.4 \text{ V}, V_{(GDNG)} = 1 \text{ V}, V_{(GDNS)} = 0 \text{ V}, VPWR = 0 \text{ V}$                                  |       | 145   |       | μΑ        |

|                         | Sinking strength oveo (salety)       | $VPWR = 1.4 \text{ V}, V_{(GDNG)} = 1 \text{ V}, V_{(GDNS)} = 0 \text{ V}, VDD = 0 \text{ V}$                                  |       | 145   |       | μΑ        |

|                         | Off-state leakage                    | $V_{(GDNS)} = 25 \text{ V}, V_{(GDNG)} \text{ open}$                                                                           |       |       | 7     | μΑ        |

| Power Cont              | rol Input (PCTRL)                    |                                                                                                                                |       |       |       |           |

| V                       | Threshold voltage <sup>(3)</sup>     | Voltage rising                                                                                                                 | 1.65  | 1.75  | 1.85  | V         |

| V <sub>(PCTRL_TH)</sub> | Tillesilolu voltage 17               | Hysteresis                                                                                                                     |       | 100   |       | mV        |

|                         | Input resistance                     | $0 \text{ V} \leq V_{(PCTRL)} \leq V_{(VAUX)}$                                                                                 | 1.5   | 2.9   | 6     | $M\Omega$ |

| Voltage Sel             | ect (HIPWR), Power Select (PSEL) (4) |                                                                                                                                |       |       |       |           |

|                         | Leakage current                      | $ \begin{array}{l} 0 \ V \leq V_{(HIPWR)} \leq V_{(DVDD)}, \\ 0 \ V \leq V_{(PSEL)} \leq V_{(DVDD)} \end{array} $              | -1    |       | 1     | μΑ        |

| Port Status             | and Voltage Control (CTL1, CTL2, UF  | P) <sup>(5)</sup>                                                                                                              |       |       |       |           |

| V <sub>OL</sub>         | Output low voltage                   | I <sub>OL</sub> = 4 mA sinking                                                                                                 |       |       | 0.4   | V         |

|                         | Leakage Current (6)                  | In Hi-Z state, $0 \le V_{(CTLx)} \le 5.5 \text{ V}$ or $0 \le V_{\overline{UFP}} \le 5.5 \text{ V}$                            | -0.5  |       | 0.5   | μΑ        |

- (1) If  $T_{J1}$  is perceived to have been exceeded an OTSD occurs and the discharge FET is disabled.

- (2) The discharge pull-down is not active in the sleep mode.

- (3) When voltage on the PCTRL pin is less than V<sub>(PCTRL TH)</sub>, the amount of power advertised is reduced by half.

- (4) Leaving HIPWR or PSEL open is an undetermined state and leads to unpredictable behavior.

- (5) These pins are high-z during a UVLO, reset, or in Sleep condition.

- (6) The pins were designed for less leakage, but testing only verifies that the leakage does not exceed 0.5 µA.

# **Electrical Characteristics (continued)**

Unless otherwise stated in a specific test condition the following conditions apply:  $-40^{\circ}\text{C} \le T_{\text{J}} \le 125^{\circ}\text{C}$ ;  $3 \le \text{VDD} \le 5.5 \text{ V}$ ,  $4.65 \text{ V} \le \text{VPWR} \le 25 \text{ V}$ ; HIPWR = GND, PSEL = GND,  $\overline{\text{GD}} = \text{VAUX}$ , PCTRL = VAUX, AGND = GND; VAUX, VTX, bypassed with  $0.1 \mu\text{F}$ , DVDD bypassed with  $0.22 \mu\text{F}$ ,  $\overline{\text{EN12V}} = \text{GND}$  and  $\overline{\text{EN9V}} = \text{GND}$ ; all other pins open (unless otherwise noted)

|                      | PARAMETER                                                 | TEST CONDITIONS                                                                          | MIN         | TYP   | MAX   | UNIT     |

|----------------------|-----------------------------------------------------------|------------------------------------------------------------------------------------------|-------------|-------|-------|----------|

| Enable 9 V           | , 12 V Capability (EN9V, EN12V)                           |                                                                                          |             |       |       |          |

|                      | Input low threshold voltage                               |                                                                                          |             |       | 0.585 | V        |

|                      | Input high threshold voltage                              |                                                                                          | 1.225       |       |       | V        |

|                      | Input hysteresis                                          |                                                                                          |             | 0.25  |       | V        |

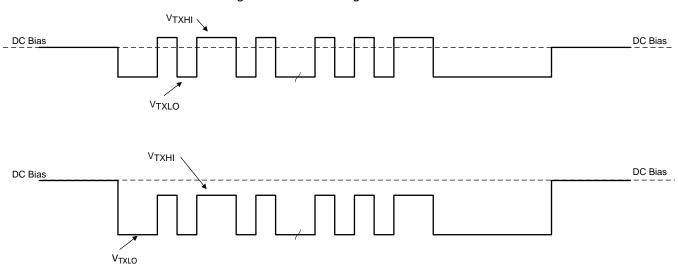

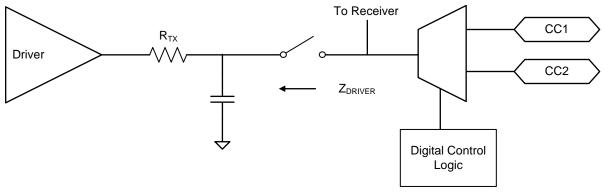

| Transmitte           | r Specifications (CC1, CC2)                               |                                                                                          |             |       |       |          |

| n                    | Output resistance (zDriver from USB PD                    | During transmission                                                                      | 22          | AF    | 75    | 0        |

| R <sub>TX</sub>      | in Documentation Support)                                 | During transmission                                                                      | 33          | 45    | 75    | Ω        |

| $V_{(TXHI)}$         | Transmit high voltage                                     | External Loading per Figure 25                                                           | 1.05        | 1.125 | 1.2   | V        |

| $V_{(TXLO)}$         | Transmit low voltage                                      | External Loading per Figure 25                                                           | <b>–</b> 75 |       | 75    | mV       |

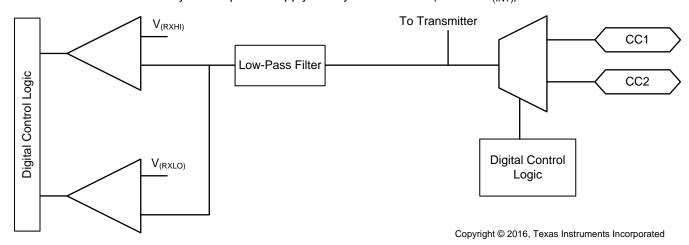

| Receiver S           | pecifications (CC1, CC2)                                  |                                                                                          |             |       |       |          |

| $V_{(RXHI)}$         | Receive threshold (rising)                                |                                                                                          | 800         | 840   | 885   | mV       |

| $V_{(RXLO)}$         | Receive threshold (falling)                               |                                                                                          | 485         | 525   | 570   | mV       |

|                      | Receive threshold (Hysteresis)                            |                                                                                          |             | 315   |       | mV       |

| V <sub>(INT)</sub>   | Amplitude of interference that can be tolerated           | Interference is 600 kHz square wave, rising 0 to 100 mV.                                 |             |       | 100   | mV       |

| (,                   | tolerated                                                 | Interference is 1 MHz sine wave                                                          |             |       | 1     | $V_{PP}$ |

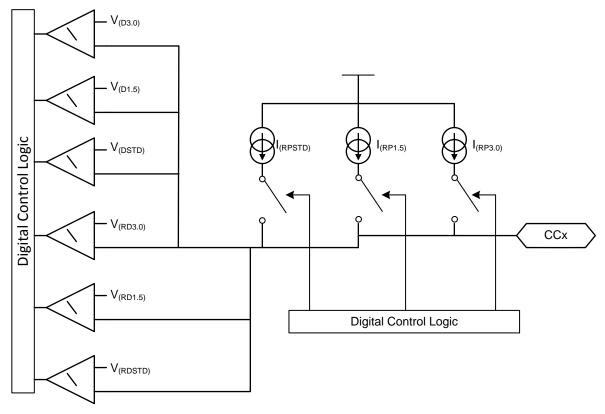

| DFP Speci            | fications (CC1, CC2)                                      |                                                                                          |             |       |       |          |

| ,                    |                                                           | In standard DFP mode (7), voltage rising                                                 | 1.52        | 1.585 | 1.65  | V        |

| V <sub>(DSTD)</sub>  |                                                           | Hysteresis                                                                               |             | 0.02  |       | V        |

|                      |                                                           | In 1.5 A DFP mode <sup>(8)</sup> , voltage rising                                        | 1.52        | 1.585 | 1.65  | V        |

| V <sub>(D1.5)</sub>  |                                                           | Hysteresis                                                                               |             | 0.02  |       | V        |

|                      |                                                           | In 3 A DFP mode <sup>(9)</sup> , voltage rising                                          | 2.50        | 2.625 | 2.75  | V        |

| V <sub>(D3.0)</sub>  |                                                           | Hysteresis                                                                               |             | 0.05  |       | V        |

| V <sub>(OCN)</sub>   |                                                           | normal mode                                                                              | 2.7         |       | 4.35  | V        |

| V <sub>(OCDS)</sub>  | Unloaded output voltage on CC pin                         | VPWR = 0 V (in UVLO) or in sleep mode                                                    | 1.8         |       | 5.5   | V        |

| (RPSTD)              |                                                           | In standard DFP mode1, CCy open,<br>0 V ≤ V <sub>CCx</sub> ≤ 1.5 V (vRd)                 | 64          | 80    | 96    | μΑ       |

| (RP1.5)              | Loaded output current while connected through CCx         | In 1.5 A DFP mode 2, CCy open,<br>0 V ≤ V <sub>CCx</sub> ≤ 1.5 V (vRd)                   | 166         | 180   | 194   | μA       |

| (RP3.0)              |                                                           | In 3 A DFP mode 3, CCy open,<br>0 V $\leq$ V <sub>CCx</sub> $\leq$ 1.5 V (vRd)           | 304         | 330   | 356   | μΑ       |

| V <sub>(RDSTD)</sub> |                                                           | In standard DFP mode1,<br>0 V ≤ V <sub>CCx</sub> ≤ 1.5 V (vRd)                           | 0.15        | 0.19  | 0.23  | V        |

|                      |                                                           | Hysteresis                                                                               |             | 0.02  |       | V        |

| V <sub>(RD1.5)</sub> | Ra, Rd detection threshold (falling)                      | In 1.5 A DFP mode2, CCy open $0 \text{ V} \leq V_{CCx} \leq 1.5 \text{ V} \text{ (vRd)}$ | 0.35        | 0.39  | 0.43  | V        |

|                      |                                                           | Hysteresis                                                                               |             | 0.02  |       | V        |

| V <sub>(RD3.0)</sub> |                                                           | In 3 A DFP mode3, CCy open $0 \text{ V} \leq V_{CCx} \leq 1.5 \text{ V} \text{ (vRd)}$   | 0.75        | 0.79  | 0.83  | V        |

| ·<br>                |                                                           | Hysteresis                                                                               |             | 0.02  |       | V        |

| V <sub>(WAKE)</sub>  | Wake threshold (rising and falling), exit from sleep mode | VPWR = 4.65 V , 0 V ≤ V <sub>DD</sub> ≤ 3 V                                              | 1.6         |       | 3.0   | V        |

| (DSDFP)              | Output current on CCx in sleep mode to detect Ra removal. | CCx = 0V, CCy floating                                                                   | 40          | 73    | 105   | μΑ       |

<sup>(7)</sup> Standard DFP mode is active after a USB Type-C sink, debug accessory, or audio accessory is attached until the first USB PD message is transmitted (after GDNG has been enabled).

Submit Documentation Feedback

<sup>(8) 1.5</sup> A DFP mode is active after a USB PD message is received.

<sup>(9) 3</sup> A DFP mode is active after GDNG has been enabled until a USB PD message is received.

### **Electrical Characteristics (continued)**

Unless otherwise stated in a specific test condition the following conditions apply:  $-40^{\circ}\text{C} \le T_{\text{J}} \le 125^{\circ}\text{C}$ ;  $3 \le \text{VDD} \le 5.5 \text{ V}$ ,  $4.65 \text{ V} \le \text{VPWR} \le 25 \text{ V}$ ; HIPWR = GND, PSEL = GND,  $\overline{\text{GD}} = \text{VAUX}$ , PCTRL = VAUX, AGND = GND; VAUX, VTX, bypassed with  $0.1 \mu\text{F}$ , DVDD bypassed with  $0.22 \mu\text{F}$ ,  $\overline{\text{EN12V}} = \text{GND}$  and  $\overline{\text{EN9V}} = \text{GND}$ ; all other pins open (unless otherwise noted)

| PARAMETER           |                                                 | TEST CONDITIONS                                                                | MIN  | TYP | MAX  | UNIT |  |

|---------------------|-------------------------------------------------|--------------------------------------------------------------------------------|------|-----|------|------|--|

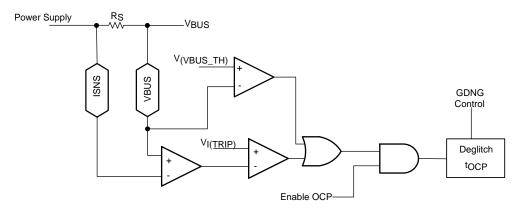

| OverCurre           | ent Protection (ISNS, VBUS)                     | ·                                                                              |      |     |      |      |  |

|                     |                                                 | Specified as $V_{(ISNS)}$ - $V_{(VBUS)}$ .<br>3.5 $V^{(10)} \le VBUS \le 25 V$ |      |     |      |      |  |

| $V_{I(TRIP)}$       | / <sub>I(TRIP)</sub> Current trip shunt voltage | HIPWR: 5 A not enabled                                                         | 19.2 |     | 22.6 | mV   |  |

|                     |                                                 | HIPWR = DVDD (5 A enabled)                                                     | 29   |     | 34   | mV   |  |

| OTSD                |                                                 |                                                                                |      |     |      |      |  |

| <b>-</b>            | Dia Tamanantana (Amalan)(11)                    | T₁↑                                                                            | 125  | 135 | 145  | 00   |  |

| T <sub>J1</sub> Die | Die Temperature (Analog) <sup>(11)</sup>        | Hysteresis                                                                     |      | 10  |      | °C   |  |

| T <sub>J2</sub>     | Dia Tamparatura (Analan) (12)                   | T₁↑                                                                            | 140  | 150 | 163  | °C   |  |

|                     | Die Temperature (Analog) (12)                   | Hysteresis                                                                     |      | 10  |      | ٠.   |  |

- (10) Common mode minimum aligns to VBUS UVLO. VBUS must be above its UVLO for the OCP function to be active.

- (11) When T<sub>J1</sub> trips a hard reset is transmitted and discharge is disabled, but the bleed discharge is not disabled.

- (12) T<sub>J2</sub> trips only when some external heat source drives the temperature up. When it trips the DVDD, and VAUX power outputs are turned off.

### 7.6 Timing Requirements

Unless otherwise stated in a specific test condition the following conditions apply:  $-40^{\circ}\text{C} \le T_{\text{J}} \le 125^{\circ}\text{C}$ ;  $3 \le \text{VDD} \le 5.5 \text{ V}$ ,  $4.65 \text{ V} \le \text{VPWR} \le 25 \text{ V}$ ; HIPWR = GND, PSEL = GND,  $\overline{\text{GD}} = \text{VAUX}$ , PCTRL = VAUX, AGND = GND; VAUX, VTX, bypassed with 0.1  $\mu\text{F}$ , DVDD bypassed with 0.22  $\mu\text{F}$ ,  $\overline{\text{EN12V}} = \text{GND}$  and  $\overline{\text{EN9V}} = \text{GND}$ ; all other pins open (unless otherwise noted)

|                     |                                                                                                    |                                                                 | MIN  | NOM | MAX  | UNIT |

|---------------------|----------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|------|-----|------|------|

| t <sub>FOVPDG</sub> | Deglitch for fast over-voltage protection                                                          |                                                                 |      | 5   |      | μs   |

| t <sub>OCP</sub>    | Deglitch Filter for over-current protection                                                        |                                                                 |      |     | 15   | μs   |

|                     | Time power is applied until CC1 and CC2 pull-ups are applied.                                      | $V_{(VPWR)} > V_{(VPWR\_TH)} OR$<br>$V_{(VDD)} > V_{(VDD\_TH)}$ |      | 2.5 | 4    | ms   |

| t <sub>CC</sub>     | Falling/Rising voltage deglitch time for detection on CC1 and CC2                                  |                                                                 |      | 120 |      | μs   |

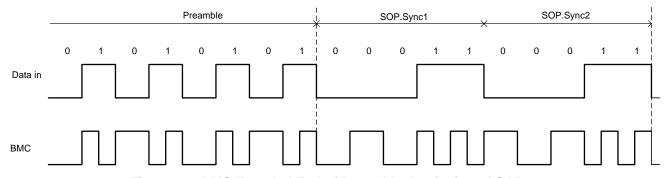

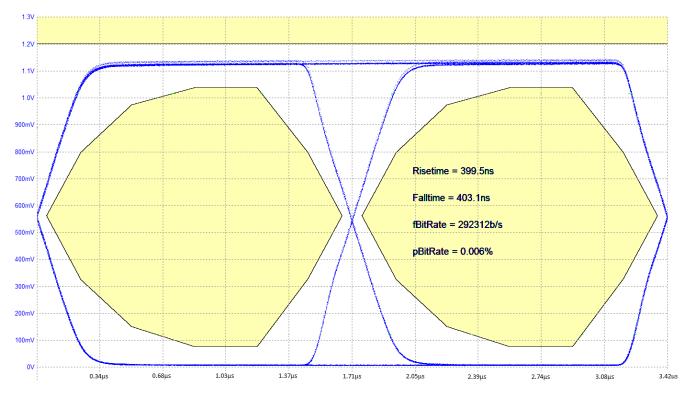

| Transmitt           | ter Specifications (CC1, CC2)                                                                      |                                                                 |      |     |      |      |

| t <sub>UI</sub>     | Bit unit Interval                                                                                  |                                                                 | 3.05 | 3.3 | 3.70 | μs   |

|                     | Rise/fall time, t <sub>Fall</sub> and t <sub>Rise</sub> (refer to USB PD in Documentation Support) | External Loading per Figure 25                                  | 300  |     | 600  | ns   |

# 7.7 Switching Characteristics

Unless otherwise stated in a specific test condition the following conditions apply:  $-40^{\circ}\text{C} \le \text{T}_{\text{J}} \le 125^{\circ}\text{C}$ ;  $3 \le \text{VDD} \le 5.5 \text{ V}$ ,  $4.65 \text{ V} \le \text{VPWR} \le 25 \text{ V}$ ; HIPWR = GND, PSEL = GND,  $\overline{\text{GD}} = \text{VAUX}$ , PCTRL = VAUX, AGND = GND; VAUX, VTX, bypassed with 0.1  $\mu$ F, DVDD bypassed with 0.22  $\mu$ F,  $\overline{\text{EN12V}} = \text{GND}$  and  $\overline{\text{EN9V}} = \text{GND}$ ; all other pins open (unless otherwise noted)

|                    | PARAMETER                                                                                                                                                                                                                                                                           | TEST CONDITIONS                                                                                                                                                                                                                 | MIN | TYP  | MAX | UNIT |

|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|------|

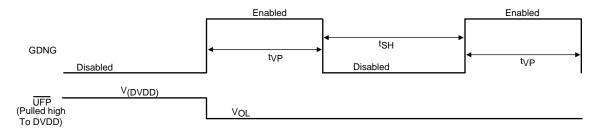

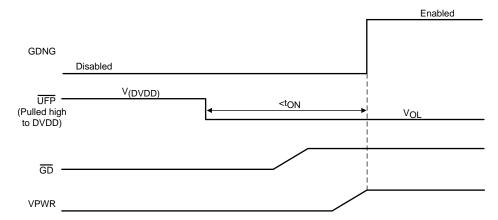

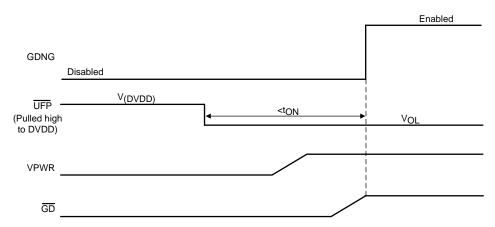

| t <sub>VP</sub>    | Delay from enabling external NFET until under-voltage and OCP protection are enabled                                                                                                                                                                                                | VBUS = GND                                                                                                                                                                                                                      |     | 190  |     | ms   |

| t <sub>STL</sub>   | Source settling time, time from CTL1 and CTL2 being changed until a PS_RDY USB PD message is transmitted to inform the sink is may draw full current. (refer to USB PD in Documentation Support)                                                                                    |                                                                                                                                                                                                                                 |     | 260  |     | ms   |

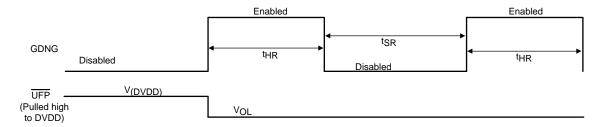

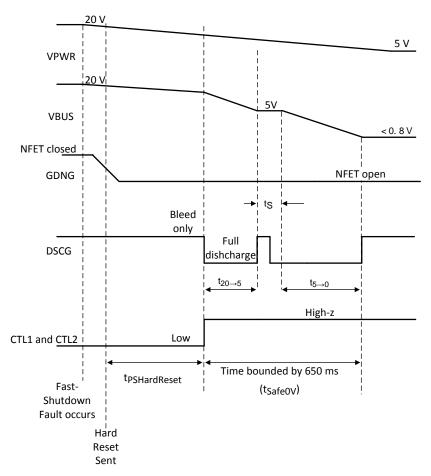

| t <sub>SR</sub>    | Time that GDNG is disabled after a hard reset. This is t <sub>SrcRecover</sub> . (refer to USB PD in Documentation Support)                                                                                                                                                         | $T_{\rm J} > T_{\rm J1}$                                                                                                                                                                                                        |     | 765  |     | ms   |

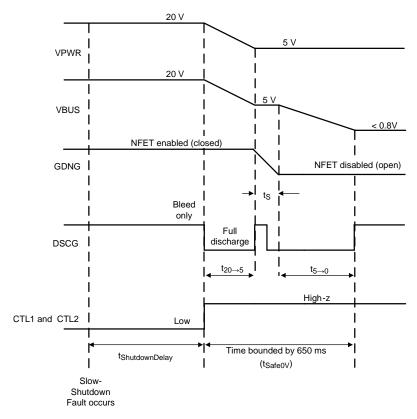

| t <sub>HR</sub>    | Time after hard reset is transmitted until GDNG is disabled. This is tpSHardReset. (refer to USB PD in Documentation Support)                                                                                                                                                       |                                                                                                                                                                                                                                 |     | 30   |     | ms   |

| t <sub>CCDeb</sub> | Time until UFP is pulled low after sink attachment, this is the USB Type-C required debounce time for attachment detection called t <sub>CCDebounce</sub> . (refer to USB Type-C in Documentation Support)                                                                          |                                                                                                                                                                                                                                 |     | 185  |     | ms   |

| t <sub>ST</sub>    | Delay after sink request is accepted until CTL1 and/or CTL2 is changed. This is called t <sub>SnkTransition</sub> . (refer to USB PD in Documentation Support)                                                                                                                      |                                                                                                                                                                                                                                 |     | 30   |     | ms   |

| t <sub>FLT</sub>   | The time in between hard reset transmissions in the presence of a persistent supply fault.                                                                                                                                                                                          | GD = GND or VPWR=GND, sink attached                                                                                                                                                                                             |     | 1395 |     | ms   |

| t <sub>SH</sub>    | The time in between retries (hard reset transmissions) in the presence of a persistent VBUS short.                                                                                                                                                                                  | VBUS = GND, sink attached                                                                                                                                                                                                       |     | 985  |     | ms   |

| t <sub>ON</sub>    | The time from UFP being pulled low until a hard reset is transmitted. Designed to be greater than t <sub>SrcTurnOn</sub> . (refer to USB PD in Documentation Support)                                                                                                               | GD = 0 V or VPWR = 0 V                                                                                                                                                                                                          |     | 600  |     | ms   |

|                    | Retry interval if USB PD sink stops communicating without being removed or if sink does not communicate after a fault condition. Time GDNG remains enabled before a hard reset is transmitted. This is the t <sub>NoResponse</sub> time. (refer to USB PD in Documentation Support) | Sink attached                                                                                                                                                                                                                   |     | 4.8  |     | s    |

| t <sub>DVDD</sub>  | Delay before DVDD is driven high                                                                                                                                                                                                                                                    | After sink attached                                                                                                                                                                                                             |     |      | 5   | ms   |

| t <sub>GDoff</sub> | Turnoff delay, time until $V_{(\underline{GDNG})}$ is below 10% of its initial value after the GD pin is low.                                                                                                                                                                       | $V_{\overline{GD}}$ : 5 V $\rightarrow$ 0 V in < 0.5 $\mu$ s.                                                                                                                                                                   |     |      | 5   | μs   |

| t <sub>FOVP</sub>  | Response time when VBUS exceeds the fast-<br>OVP threshold                                                                                                                                                                                                                          | VBUS ↑ to GDNG OFF (V <sub>(GDNG)</sub> below 10% its initial value)                                                                                                                                                            |     |      | 30  | μs   |

|                    | OCP large signal response time                                                                                                                                                                                                                                                      | 5 A enabled, $V_{(ISNS)}$ - $V_{(VBUS)}$ : 0 V $\rightarrow$ 42 mV measured to GDNG transition start.                                                                                                                           |     |      | 30  | μs   |

|                    | Time until discharge is stopped after T <sub>J1</sub> is exceeded.                                                                                                                                                                                                                  | 0 V ≤ V <sub>(DSCG)</sub> ≤ 25 V                                                                                                                                                                                                |     |      | 10  | μs   |

|                    | Digital output fall time                                                                                                                                                                                                                                                            | $\begin{array}{l} V_{(PULLUP)} = 1.8 \text{ V, } C_L = 10 \text{ pF,} \\ R_{(PULLUP)} = 10 \text{ k}\Omega, V_{(CTLx)} \text{ or} \\ V_{(\overline{UFP})} : 70\% \text{ V}_{PULLUP} \rightarrow 30\% \\ V_{PULLUP} \end{array}$ | 20  |      | 300 | ps   |

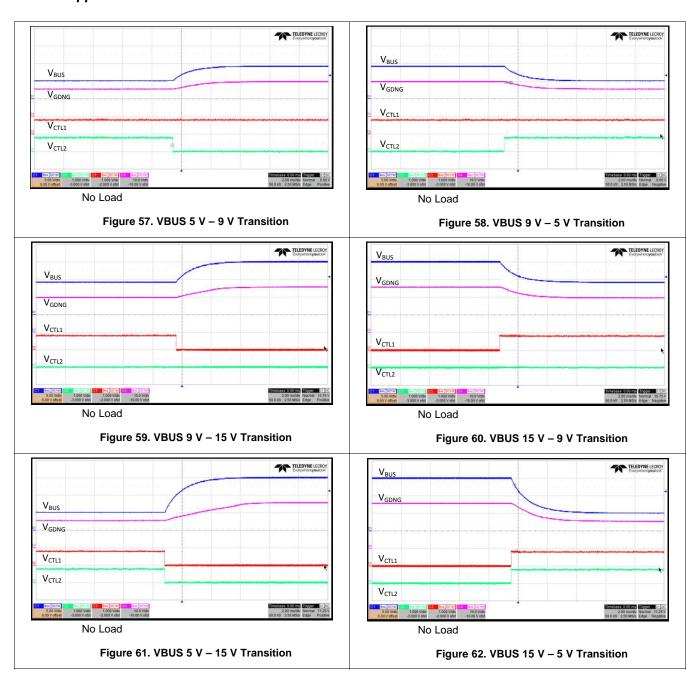

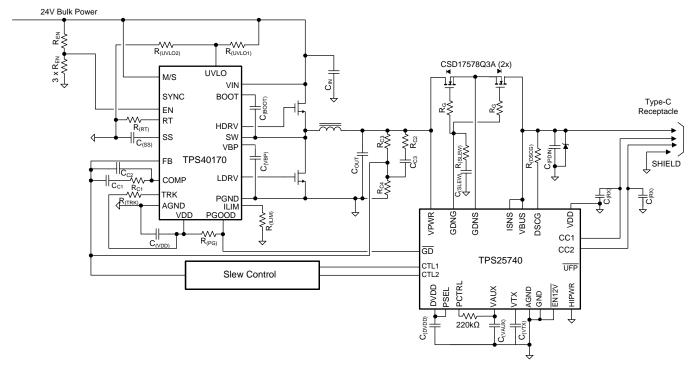

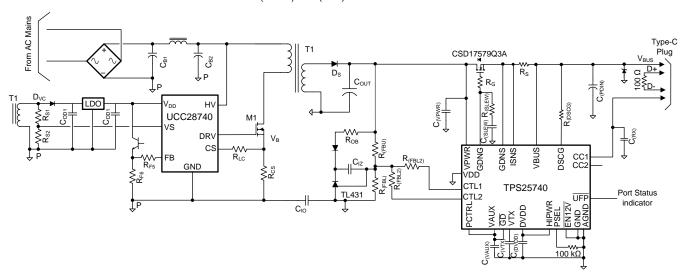

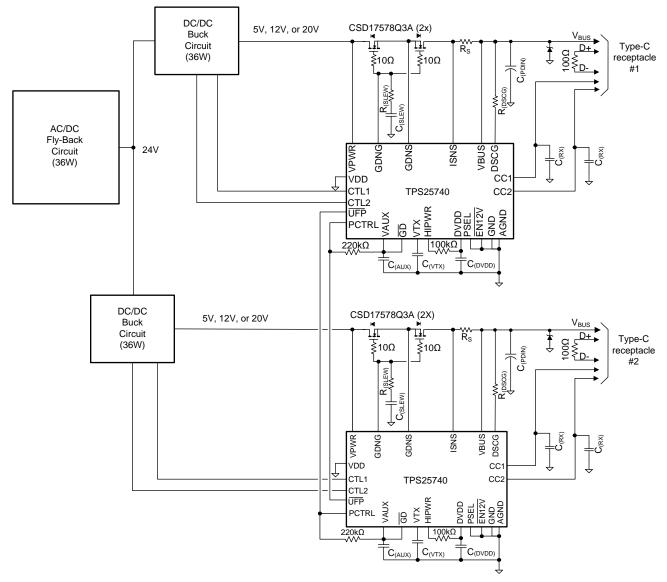

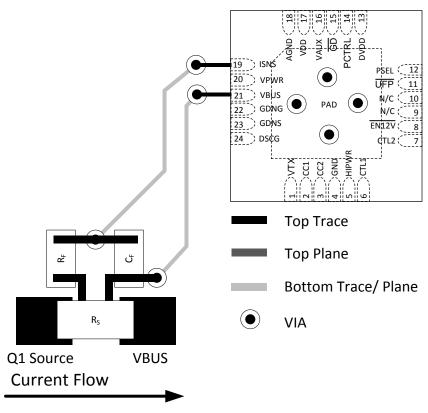

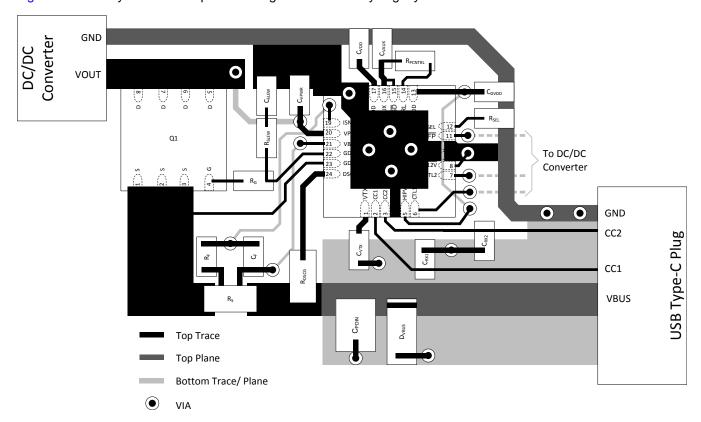

Submit Documentation Feedback